#### **Developer Note**

# Power Macintosh Computers

Power Macintosh 6100/60 Power Macintosh 6100/60AV Power Macintosh 7100/66 Power Macintosh 7100/66AV Power Macintosh 8100/80 Power Macintosh 8100/80AV

Developer Press © Apple Computer, Inc. 1994

#### ♣ Apple Computer, Inc. © 1994, Apple Computer, Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, mechanical, electronic, photocopying, recording, or otherwise, without prior written permission of Apple Computer, Inc. Printed in the United States of America.

The Apple logo is a registered trademark of Apple Computer, Inc. Use of the "keyboard" Apple logo (Option-Shift-K) for commercial purposes without the prior written consent of Apple may constitute trademark infringement and unfair competition in violation of federal and state laws.

No licenses, express or implied, are granted with respect to any of the technology described in this book. Apple retains all intellectual property rights associated with the technology described in this book. This book is intended to assist developers to develop products only for use with Apple Macintosh computers.

Apple Computer, Inc. 20525 Mariani Avenue Cupertino, CA 95014 408-996-1010

Simultaneously published in the United States and Canada.

Apple, the Apple logo, APDA, AppleLink, AppleTalk, LocalTalk, Macintosh, Macintosh Quadra, PowerBook, and Power Macintosh are trademarks of Apple Computer, Inc., registered in the United States and other countries.

Apple Desktop Bus, Apple SuperDrive, AudioVision, GeoPort, Macintosh Centris, and QuickTime are trademarks of Apple Computer, Inc.

Adobe Illustrator and PostScript are trademarks of Adobe Systems Incorporated, which may be registered in certain jurisdictions.

America Online is a service mark of Quantum Computer Services, Inc. CompuServe is a registered trademark of CompuServe, Inc.

FrameMaker is a registered trademark of Frame Technology Corporation.

Helvetica and Palatino are registered trademarks of Linotype Company.

Intel is a trademark of Intel Corporation.

Internet is a trademark of Digital Equipment Corporation.

ITC Zapf Dingbats is a registered trademark of International Typeface Corporation.

Microsoft is a registered trademark and Windows is a trademark of Microsoft Corporation.

Motorola is a registered trademark of Motorola Corporation.

NuBus is a trademark of Texas Instruments.

Pentium is a trademark of Intel Corporation.

PowerPC is a trademark of IBM Corporation.

RCA is a registered trademark of Radio Corporation of America.

SoftPC and SoftWindows are registered trademarks of Insignia Solutions, Inc.

# LIMITED WARRANTY ON MEDIA AND REPLACEMENT

If you discover physical defects in the manual or in the media on which a software product is distributed, APDA will replace the media or manual at no charge to you provided you return the item to be replaced with proof of purchase to APDA.

ALL IMPLIED WARRANTIES ON THIS MANUAL, INCLUDING IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, ARE LIMITED IN DURATION TO NINETY (90) DAYS FROM THE DATE OF THE ORIGINAL RETAIL PURCHASE OF THIS PRODUCT.

Even though Apple has reviewed this manual, APPLE MAKES NO WARRANTY OR REPRESENTATION, EITHER EXPRESS OR IMPLIED, WITH RESPECT TO THIS MANUAL, ITS QUALITY, ACCURACY, MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE. AS A RESULT, THIS MANUAL IS SOLD "AS IS," AND YOU, THE PURCHASER, ARE ASSUMING THE ENTIRE RISK AS TO ITS QUALITY AND ACCURACY.

IN NO EVENT WILL APPLE BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES RESULTING FROM ANY DEFECT OR INACCURACY IN THIS MANUAL, even if advised of the possibility of such damages.

THE WARRANTY AND REMEDIES SET FORTH ABOVE ARE EXCLUSIVE AND IN LIEU OF ALL OTHERS, ORAL OR WRITTEN, EXPRESS OR IMPLIED. No Apple dealer, agent, or employee is authorized to make any modification, extension, or addition to this warranty.

Some states do not allow the exclusion or limitation of implied warranties or liability for incidental or consequential damages, so the above limitation or exclusion may not apply to you. This warranty gives you specific legal rights, and you may also have other rights which vary from state to state.

# Contents

Figures and Tables vii

| Preface   | About This Developer Note ix                                                                                                                                                                                                                                                                                                                                                             |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Contents of This Note ix  Supplementary Documents x  Apple Publications x  Other Publications xii  Conventions and Abbreviations xii  Typographical Conventions xii  Standard Abbreviations xiii                                                                                                                                                                                         |

| Chapter 1 | Introduction 1                                                                                                                                                                                                                                                                                                                                                                           |

|           | The First Generation of Power Macintosh 2 Models and Configurations 3 Disk Storage and RAM 3 Audio and Video Features 5 Apple Expansion Cards 7 I/O Accessories 8 Features and Capabilities 8 Machine Identification 10                                                                                                                                                                  |

| Chapter 2 | Hardware Overview 11                                                                                                                                                                                                                                                                                                                                                                     |

|           | Physical Forms 12 System Architecture 12 Functional Units—Main Circuit Board 14 Main Processor 14 Read-Only Memory 14 Random-Access Memory 14 Cache Memory 15 High-Speed Memory Controller 15 Apple Memory-Mapped I/O Controller 15 Data Path Chips 16 Ariel II Video Chip 16 SWIM III Floppy Disk Drive Controller 16 Curio I/O Chip 17 Cuda Microcontroller Chip 17 AWAC Sound Chip 17 |

**BART NuBus Controller** 17 Squidlet Chip 17 Functional Units—AV Card 18 Cyclone Integrated Video Interfaces Controller 18 Sebastian Chip 18 SAA7194 Decoder 19 19 Mickey Encoder System Clocks **CPU Bus CPU Bus Arbitration** 20 **Address Errors** 21 Memory Management Memory Organization 21 Physical Memory Allocations 22 **RAM Access** 22 Interrupt Handling 22

## Chapter 3 Input and Output Interfaces 25

**External Device Interfaces** 26 Apple Desktop Bus 26 **Ethernet Port** Serial Ports 28 SCSI Connection 29 **Power Budgets** 29 Internal SCSI Locations 30 Pin Assignments Automatic SCSI Termination 33 Installing Internal SCSI Devices 34 Floppy Disk Drive Connection 34 Built-in Interface for Video Monitors 35 AudioVision Monitor Support 36 **Monitor Output Timing** 38 **VRAM Expansion Cards** 39 AV Card Video Output 43 Video Inputs 45 Sound I/O

| Chapter 4  | Expansion Capabilities 49                                                                                                                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | NuBus Interface 50 NuBus Slot Connections 51 NuBus Cards for the Power Macintosh 6100/60 52 DAV Interface 53 PDS Expansion Cards for the Power Macintosh 6100/60 54 RAM Expansion SIMMs 57 Cache Expansion SIMMs 60 VRAM Expansion SIMMs 61 |

| Appendix A | Overview of PowerPC Technology 67                                                                                                                                                                                                           |

|            | The Advantages of RISC 67 PowerPC Architecture 69 Instruction Queue 69 Branch Unit 70 Processing Units 70 Data Cache 71 Data Organization 71 The PowerPC Microprocessor Family 74                                                           |

| Appendix B | Power Macintosh Application Development 75                                                                                                                                                                                                  |

|            | Building New Software 75 Converting Existing Software 76 Application Performance and System Requirements 76 System Software Additions 77 DOS/Windows Emulation 77                                                                           |

|            | Glossary 79                                                                                                                                                                                                                                 |

|            | Index 83                                                                                                                                                                                                                                    |

# Figures and Tables

| Chapter 1 | Introduction           | 1                                                                       |

|-----------|------------------------|-------------------------------------------------------------------------|

|           | Table 1-1<br>Table 1-2 | Configurations of Power Macintosh computers 4 Expansion capabilities 5  |

|           | Table 1-3              | VRAM capacities and video I/O support 6                                 |

|           | Table 1-4              | Monitors supported by various VRAM sizes 6                              |

|           | Table 1-5              | CPU identification 10                                                   |

| Chapter 2 | Hardware Ove           | erview 11                                                               |

|           | Figure 2-1             | Block diagram for Power Macintosh 8100/80 13                            |

|           | Figure 2-2             | Emulated interrupt handling 23                                          |

|           | Table 2-1              | External dimensions 12                                                  |

|           | Table 2-2              | Model-specific clocks 19                                                |

|           | Table 2-3              | Fixed-rate system clocks 20                                             |

|           | Table 2-4              | CPU bus arbitration order 20                                            |

|           | Table 2-5              | Physical memory allocations 22                                          |

| Chapter 3 | Input and Out          | put Interfaces 25                                                       |

| •         | Figure 3-1             | ADB socket 27                                                           |

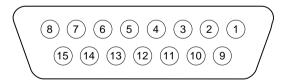

|           | Figure 3-2             | Serial port connector 28                                                |

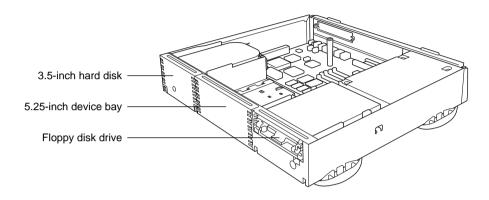

|           | Figure 3-3             | Power Macintosh 6100/60 and 6100/60AV internal SCSI device locations 30 |

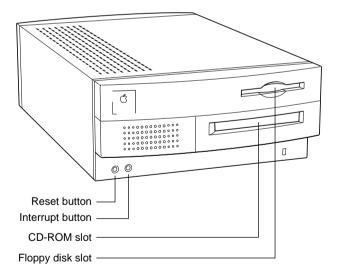

|           | Figure 3-4             | Power Macintosh 7100/66 and 7100/66AV CD-ROM location 30                |

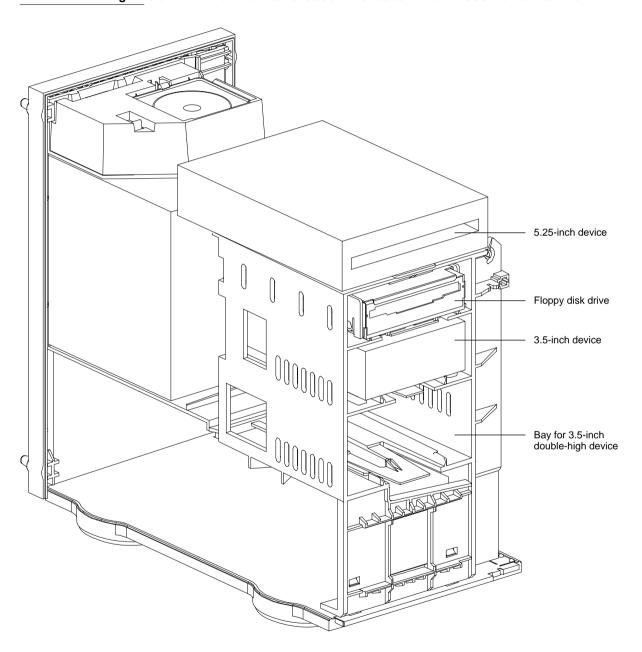

|           | Figure 3-5             | Power Macintosh 8100/80 and 8100/80AV internal SCSI device locations 31 |

|           | Figure 3-6             | SCSI bus terminators 33                                                 |

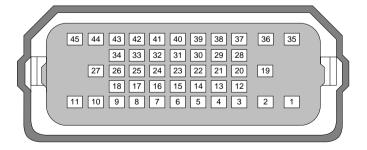

|           | Figure 3-7             | AudioVision monitor connector 36                                        |

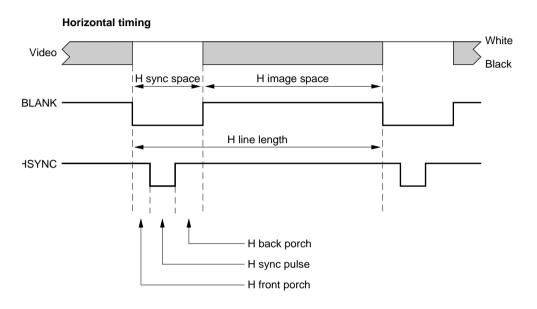

|           | Figure 3-8             | Video timing diagram 38                                                 |

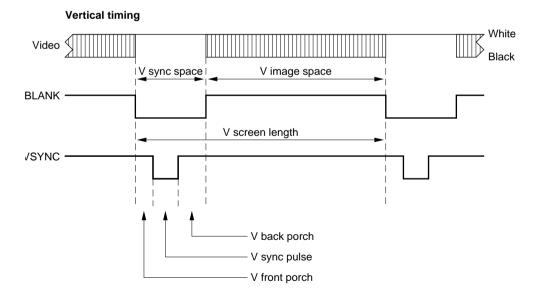

|           | Figure 3-9             | DB-15 video monitor connector 40                                        |

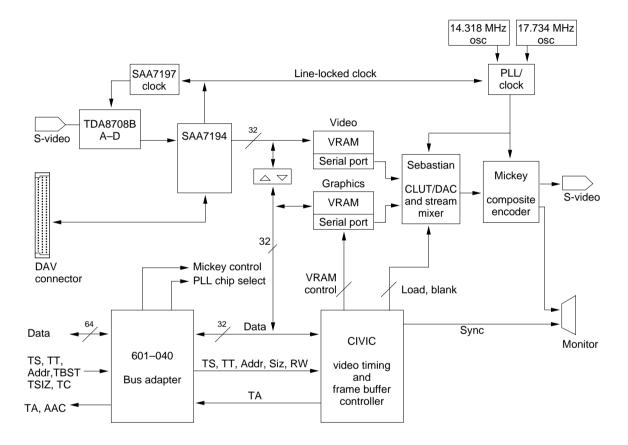

|           | Figure 3-10            | AV card block diagram 42                                                |

|           | Figure 3-11            | Video input and output connectors 44                                    |

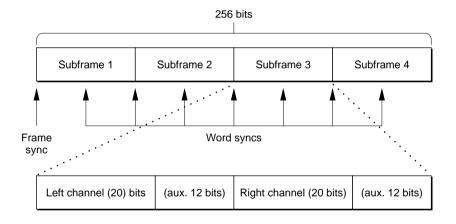

|           | Figure 3-12            | AWAC sound frame 47                                                     |

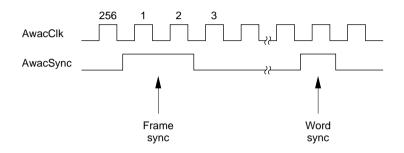

|           | Figure 3-13            | Sound frame and word synchronization 48                                 |

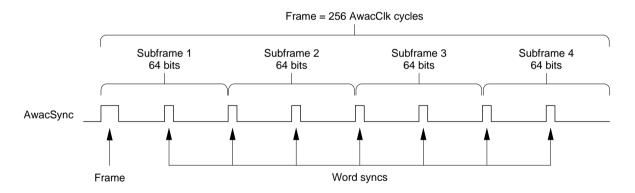

|           | Figure 3-14            | Sound subframe synchronization 48                                       |

|           | Table 3-1              | ADB pin assignments 27                                                  |

|           | Table 3-2              | Ethernet port pin assignments 27                                        |

|           | Table 3-3              | Serial port pin assignments 28                                          |

|           | Table 3-4              | Spaces for internal SCSI devices 29                                     |

|           | Table 3-5              | SCSI power budget 29                                                    |

|           | Table 3-6              | SCSI pin assignments 32                                                 |

|           | Table 3-7              | Floppy disk drive connector pin assignments 34                          |

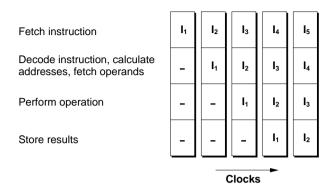

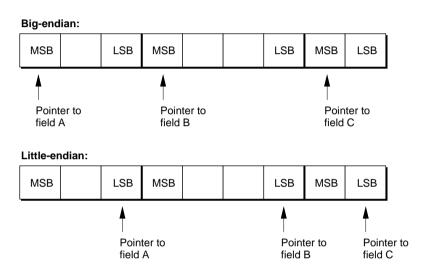

|            | Figure A-1<br>Figure A-2<br>Figure A-3 | PowerPC 601 architecture 69 Instruction pipelining 71 Big-endian and little-endian addressing 72 |

|------------|----------------------------------------|--------------------------------------------------------------------------------------------------|

| Appendix A | Overview of                            | PowerPC Technology 67                                                                            |

|            | Table 4-9                              | VRAM SIMM pin assignments 62                                                                     |

|            | Table 4-8                              | Cache SIMM pin assignments 60                                                                    |

|            | Table 4-7                              | RAM SIMM pin assignments 58                                                                      |

|            | Table 4-6                              | RAM configurations 57                                                                            |

|            | Table 4-5                              | PDS connector pin assignments 55                                                                 |

|            | Table 4-4                              | DAV connector pin assignments 54                                                                 |

|            | Table 4-3                              | Power budget for each NuBus card 52                                                              |

|            | Table 4-2                              | NuBus pin assignments 51                                                                         |

|            | Table 4-1                              | Maximum expansion card capacity 50                                                               |

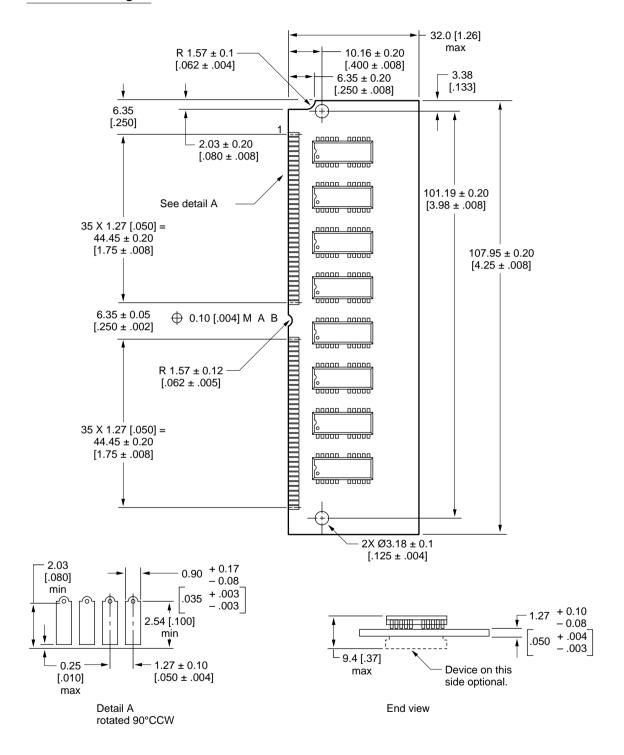

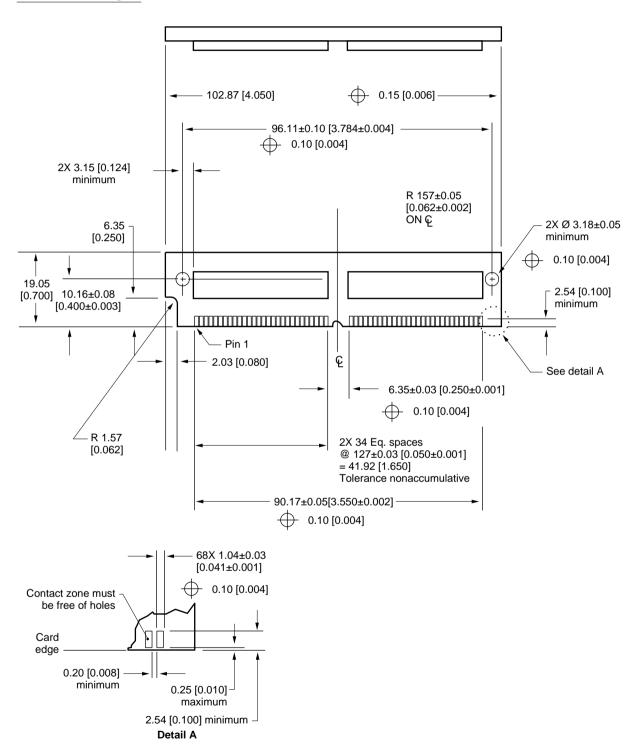

|            | Figure 4-3                             | VRAM SIMM mechanical dimensions 63                                                               |

|            | Figure 4-2                             | RAM SIMM mechanical dimensions 59                                                                |

|            | Figure 4-1                             | Power Macintosh 6100 NuBus adapter card mounting 53                                              |

| Chapter 4  | Expansion C                            | Capabilities 49                                                                                  |

|            | Table 3-10                             | 1 DO CONNECTON SOUND SIGNAIS 41                                                                  |

|            | Table 3-15                             | PDS connector sound signals 47                                                                   |

|            | Table 3-14<br>Table 3-15               | Pin assignments for video I/O connectors 45 Sound connections 46                                 |

|            | Table 3-13                             | Monitor color depths 43                                                                          |

|            | Table 3-12                             | DB-15 video monitor pin assignments 41                                                           |

|            | Table 3-11                             | Monitors supported by VRAM expansion cards 40                                                    |

|            | Table 3-10                             | Apple monitor timing values 39                                                                   |

|            | Table 3-9                              | AudioVision connector pin assignments 37                                                         |

Monitors supported by built-in video

36

Table 3-8

# About This Developer Note

This developer note introduces the Power Macintosh family, Apple Computer's first Macintosh computers that use the PowerPC microprocessor. It is written primarily for experienced Macintosh hardware and software developers who want to create products that are compatible with these computers.

The discussion assumes that you are already familiar with the general technology of Macintosh computers. If you are unfamiliar with Macintosh technology or would like more technical information, you may want to obtain copies of the related technical documents listed in "Supplementary Documents," later in this preface.

This note is published in two forms: an online version included with the Apple Developer CD and a looseleaf paper version published by APDA. For information about APDA, see "Supplementary Documents," later in this preface.

### Contents of This Note

This developer note is divided into four chapters:

- Chapter 1, "Introduction," presents an overview of the features of Power Macintosh computers, the configurations in which they are offered, and the differences between them and other Macintosh computers.

- Chapter 2, "Hardware Overview," describes the Power Macintosh circuit boards, including their functional units, signal timing, memory management, and other general characteristics.

- Chapter 3, "Input and Output Interfaces," describes the interfaces of Power Macintosh computers with peripheral equipment, including details of signal handling, connectors, and pin assignments.

- Chapter 4, "Expansion Capabilities," contains interface specifications for plug-in expansion cards compatible with Power Macintosh computers, with details of card configuration and pin assignments.

Two appendixes follow the main part of this note:

- Appendix A, "Overview of PowerPC Technology," gives some of the background of the PowerPC RISC microprocessor and tells how it differs from CISC processors such as the Motorola MC68040 and the Intel processors.

- Appendix B, "Power Macintosh Application Development," summarizes the process of developing application software to run on Power Macintosh computers. More detailed information is given in *Inside Macintosh: PowerPC System Software* and *Building Programs for PowerPC Processor—Based Macintosh Computers*. These books are listed in "Supplementary Documents," later in this preface.

At the end of this developer note are a glossary and an index.

# Supplementary Documents

The following documents provide information that complements or extends the information in this developer note.

## **Apple Publications**

*Inside Macintosh* is a collection of books, organized by topic, that describe the system software of Macintosh computers. Together, these books provide the essential reference for programmers, software designers, and engineers. Current volumes include the following titles:

Inside Macintosh: Overview

Inside Macintosh: Macintosh Toolbox Essentials Inside Macintosh: More Macintosh Toolbox

Inside Macintosh: Files Inside Macintosh: Processes Inside Macintosh: Memory

Inside Macintosh: Operating System Utilities Inside Macintosh: Imaging With QuickDraw

Inside Macintosh: Text

Inside Macintosh: Interapplication Communication

Inside Macintosh: Devices

Inside Macintosh: QuickTime

*Inside Macintosh: QuickTime Components*

Inside Macintosh: Networking

*Inside Macintosh: PowerPC System Software* covers in detail the changes and extensions to Macintosh system software version 7.1 for Power Macintosh computers, including the run-time architecture and new Macintosh Toolbox managers.

Building Programs for PowerPC Processor—Based Macintosh Computers is a general discussion for developers of the development and building of application software for PowerPC processor—based Macintosh systems, including Power Macintosh computers.

*Technical Introduction to the Macintosh Family,* second edition, surveys the complete Macintosh family of computers from the developer's point of view.

Macintosh Human Interface Guidelines provides authoritative information on the theory behind the Macintosh "look and feel" and Apple's standard ways of using individual interface components.

*Making It Macintosh* is an interactive guide to human-computer interface design for Macintosh software. This CD-ROM disc contains more than 100 animated examples that demonstrate the correct use of Macintosh human interface elements.

Designing Cards and Drivers for the Macintosh Family, third edition, explains the hardware and software requirements for drivers and NuBus<sup>™</sup> '90 expansion cards compatible with Macintosh computers, including the Power Macintosh computers covered by this developer note.

Technical Note 144 (*Macintosh Color Monitor Connections*) and Technical Note 326 (*M.HW.SenseLines*) provide technical details of the interfaces to various Apple and third-party monitors.

The *NuBus Block Transfers* technical note provides information about block data transfers to and from NuBus expansion cards.

*Macintosh Developer Note Number 5* contains both hardware and system software details for the Macintosh Quadra 840AV and Macintosh Centris 660AV computers, which feature the Apple AV technologies.

Macintosh Developer Note Number 8 includes Macintosh DAV Interface for NuBus Expansion Cards, a developer note that describes how expansion cards can access digital audio-video data in Power Macintosh AV computers.

The Apple publications listed above are available from APDA. APDA is Apple's worldwide source for over three hundred development tools, technical resources, training products, and information for anyone interested in developing applications on Apple platforms. Customers receive the quarterly *APDA Tools Catalog* featuring all current versions of Apple development tools and the most popular third-party development tools. Ordering is easy; there are no membership fees, and application forms are not required for most products. APDA offers convenient payment and shipping options, including site licensing.

To order products or to request a complimentary copy of the *APDA Tools Catalog*, contact

**APDA**

Apple Computer, Inc.

P.O. Box 319

Buffalo, NY 14207-0319

Telephone 800-282-2732 (United States)

800-637-0029 (Canada) 716-871-6555 (International)

Fax 716-871-6511

AppleLink APDA

America Online APDA

CompuServe 76666,2405

Internet APDA@applelink.apple.com

#### Other Publications

The following documents are available from the organizations listed:

#### Comité Consultatif International Radio (CCIR):

Recommended Standard 601-2

#### Institute for Electrical and Electronics Engineers (IEEE):

Standard 1196

#### IT&T:

ASCO 2300 Audio-Stereo Codec Specification

#### Motorola:

PowerPC 601 RISC Microprocessor User's Manual

## Conventions and Abbreviations

This developer note uses the following typographical conventions and abbreviations.

## Typographical Conventions

New terms appear in **boldface** where they are first defined.

Computer-language text—any text that is literally the same as it appears in computer input or output—appears in Courier font.

Hexadecimal numbers are preceded by a dollar sign (\$). For example, the hexadecimal equivalent of decimal 16 is written as \$10.

#### Note

A note like this contains information that is interesting but not essential for an understanding of the text. ◆

#### **IMPORTANT**

A note like this contains important information that you should read before proceeding.  $\mbox{\ } \Delta$

#### ▲ WARNING

A note like this directs your attention to something that could cause damage or result in a loss of data. ▲

#### Standard Abbreviations

Abbreviations for standard units of measure used in this developer note include

A MHz megahertz amperes cm centimeters mm millimeters dΒ decibels milliseconds ms GB gigabytes mV millivolts Hz Hertz nanoseconds ns KB kilobytes рF picofarads Kbit kilobits sec. seconds kHz kilohertz V volts kΩ kilohms μF microfarads mΑ milliamperes microseconds μsec MB megabytes Ω ohms

Other abbreviations used in this developer note include

AC alternating current

ADB Apple Desktop Bus

ADC analog-to-digital converter

AGND analog ground

megabits

Mbit

AMIC Apple Memory-Mapped Input/Output Controller

API application programming interface

ASIC application-specific integrated circuit

AWAC audio waveform amplifier and converter

CAS column address strobe

CCIR Comité Consultatif International Radio

CD-ROM compact disc read-only memory

CISC complex instruction set computing

CIVIC Cyclone Integrated Video Interfaces Controller

CLUT color lookup table

CMOS complementary metal-oxide semiconductor

CPU central processing unit

DAC digital-to-analog converter

DC direct current

DMA direct memory access

DP data path

DRAM dynamic random-access memory

#### PREFACE

EMI electromagnetic interference

FIFO first-in, first-out

GCR Group Code Recording

GND ground

HMC high-speed memory controller

HPV high-performance video

IEEE Institute of Electrical and Electronics Engineers

I/O input/output

ISDN Integrated Services Digital Network

MACE Media Access Controller for Ethernet

MFM Modified Frequency Modulation

MMU memory management unit

n.a. not applicableNC no connection

PAL Phased Alternate Lines

PBX Private Branch Exchange

PDS processor-direct slot

RAM random-access memory

RAS row address strobe

RGB red-green-blue

RISC reduced instruction set computing

rms root mean square ROM read-only memory

SCC Serial Communications Controller SCSI Small Computer System Interface SIMM Single Inline Memory Module

SNR signal-to-noise ratio

VCR videocassette recorder

VIA Versatile Interface Adapter

VRAM video random-access memory

Power Macintosh 6100/60, 6100/60AV, 7100/66, 7100/66AV, 8100/80, and 8100/80AV computers represent the first generation of products in Apple Computer's transition to reduced instruction set computing (RISC), using the PowerPC 601 microprocessor. RISC technology increases computing speed dramatically. Even the low end of the Power Macintosh family, the competitively priced Power Macintosh 6100/60, delivers more than twice the performance of any previous Macintosh computer.

This chapter describes the first generation of Power Macintosh computers in general terms and lists some of their features and differences. For a discussion of Apple's RISC technology in general, see Appendix A, "Overview of PowerPC Technology."

## The First Generation of Power Macintosh

The first generation of Power Macintosh computers consists of three fast, powerful desktop models with nearly identical electronic circuitry. Their principal differences are their processor speeds and mechanical configurations:

- The Power Macintosh 6100/60 and 6100/60AV run at 60 MHz and are housed in a low-profile enclosure designed to be placed under the user's monitor. In physical form they resemble the Macintosh Quadra 610 and Macintosh Centris 660AV.

- The Power Macintosh 7100/66 and 7100/66AV run at 66 MHz and are housed in a mid-size enclosure similar to that of the Macintosh II and Macintosh Quadra 650.

- The Power Macintosh 8100/80 and 8100/80AV run at 80 MHz and are housed in a minitower enclosure, like that of the Macintosh Quadra 800 and 840AV. The minitower design provides more room for internal disk drives and expansion cards.

The Power Macintosh model designations ending in AV are configurations that support the video capture and output features of the Apple AV Technologies.

Principal hardware features of the Power Macintosh 6100/60, 7100/66, and 8100/80 include

- a PowerPC 601 RISC microprocessor

- built-in video output for standard monitors

- provision for NuBus<sup>™</sup> and processor-direct expansion cards

- built-in Ethernet support

- built-in GeoPort support, compatible with most telephone systems

- high-quality 16-bit stereo sound input and output

- a wide range of RAM, disk drive, and CD-ROM configurations

Besides these capabilities, the Power Macintosh 6100/60AV, 7100/66AV, and 8100/80AV provide sophisticated video I/O processing facilities. These and other features are discussed further in "Features and Capabilities," later in this chapter. Chapter 2, "Hardware Overview," provides more detailed hardware information. For a summary of Power Macintosh software, see Appendix B, "Power Macintosh Application Development."

# Models and Configurations

Power Macintosh computers have many common features. They differ mainly in physical form, speed, and expansion facilities:

- The Power Macintosh 6100/60 and 6100/60AV, the least expensive models in the family, are housed in a low-profile enclosure similar to that of the Macintosh Quadra 610 and Centris 660AV. They run at 60 MHz and have one processor-direct slot (PDS) for an expansion card. To add NuBus capability to the Power Macintosh 6100/60, the user installs the Power Macintosh 6100 NuBus™ adapter card. The Power Macintosh 6100/60 is shipped with its expansion slot empty; the Power Macintosh 6100/60AV is shipped with an AV card installed. Both models have built-in support for a variety of monitors, including Apple AudioVision displays. The Power Macintosh 6100 NuBus adapter card and AV card are described in "Apple Expansion Cards," later in this chapter.

- The Power Macintosh 7100/66 and 7100/66AV are housed in a full-sized desktop configuration similar to that of the Macintosh IIvx and Macintosh Quadra 650. They run at 66 MHz and have three NuBus slots for expansion cards plus a separate processor-direct slot (PDS) for extending their video capabilities. Besides built-in display support, the Power Macintosh 7100/66 is shipped with a VRAM expansion card installed and the Power Macintosh 7100/66AV is shipped with an AV card installed.

- The Power Macintosh 8100/80 and 8100/80AV are housed in a minitower configuration similar to that of the Macintosh Quadra 800 and 840AV. They run at 80 MHz and have three NuBus slots for expansion cards plus a separate PDS for extending their video capabilities. Besides built-in display support, the Power Macintosh 8100/80 is shipped with a VRAM expansion card installed and the Power Macintosh 8100/80AV is shipped with an AV card installed. Both models are shipped with second-level cache memory installed.

For details of the monitor and video I/O support provided by various Power Macintosh models, see "Audio and Video Features," later in this chapter.

# Disk Storage and RAM

All Power Macintosh computers include a new version of the Apple SuperDrive floppy disk drive that conforms to common industry practice by not including the automatic disk injection feature of previous versions of the Apple SuperDrive. It is capable of accepting floppy disks up to 1.44 MB capacity.

The user can add a variety of external disk drives to any Power Macintosh computer by using the external SCSI port. For details of the possible SCSI configurations, see "SCSI Connection," in Chapter 3.

The specific shipping configurations for the first generation of Power Macintosh computers are listed in Table 1-1 on page 4. Bundled expansion cards are described in "Apple Expansion Cards," later in this chapter.

Table 1-1 Configurations of Power Macintosh computers

| Catalog number                   | RAM size                        | Hard disk<br>drive size | Built-in<br>CD-ROM | Bundled PDS<br>expansion card |  |  |  |

|----------------------------------|---------------------------------|-------------------------|--------------------|-------------------------------|--|--|--|

| Power Macintosh 610              | Power Macintosh 6100/60 models: |                         |                    |                               |  |  |  |

| M2196LL/A                        | 8 MB                            | 160 MB                  | No                 | None                          |  |  |  |

| M2197LL/A                        | 8 MB                            | 160 MB                  | Yes                | None                          |  |  |  |

| M1878LL/A                        | 8 MB                            | 250 MB                  | Yes                | None                          |  |  |  |

| Power Macintosh 610              | 00/60AV model:                  |                         |                    |                               |  |  |  |

| M2738LL/A                        | 8 MB                            | 250 MB                  | Yes                | AV                            |  |  |  |

| Power Macintosh 710              | 00/66 models:                   |                         |                    |                               |  |  |  |

| M2464LL/A                        | 8 MB                            | 250 MB                  | No                 | VRAM expansion                |  |  |  |

| M2465LL/A                        | 8 MB                            | 250 MB                  | Yes                | VRAM expansion                |  |  |  |

| M2466LL/A                        | 8 MB                            | 500 MB                  | Yes                | VRAM expansion                |  |  |  |

| Power Macintosh 710              | 00/66AV model:                  |                         |                    |                               |  |  |  |

| M2467LL/A                        | 8 MB                            | 500 MB                  | Yes                | AV                            |  |  |  |

| Power Macintosh 810              | 00/80 models:                   |                         |                    |                               |  |  |  |

| M1884LL/A                        | 8 MB                            | 250 MB                  | No                 | VRAM expansion                |  |  |  |

| M2199LL/A                        | 16 MB                           | 500 MB                  | No                 | VRAM expansion                |  |  |  |

| M2284LL/A                        | 16 MB                           | 500 MB                  | Yes                | VRAM expansion                |  |  |  |

| M2294LL/A                        | 16 MB                           | 1 GB                    | No                 | VRAM expansion                |  |  |  |

| Power Macintosh 8100/80AV model: |                                 |                         |                    |                               |  |  |  |

| M2293LL/A                        | 16 MB                           | 500 MB                  | Yes                | AV                            |  |  |  |

|                                  |                                 |                         |                    |                               |  |  |  |

The user can expand the RAM capacity of any Power Macintosh computer by installing Single Inline Memory Module (SIMM) cards. Including RAM expansion, there are a wide range of options for expanding and reconfiguring computers of the Power Macintosh family. Some important options are summarized in Table 1-2.

All Power Macintosh models support secondary cache expansion to 256 KB; this expansion is standard with the Power Macintosh 8100/80 and 8100/80AV.

RAM SIMMs must be installed in pairs. Possible RAM configurations in Power Macintosh computers are shown in Table 4-6 on page 57.

For more detailed information about user expansion of Power Macintosh computers, see Chapter 4, "Expansion Capabilities."

Table 1-2 Expansion capabilities

|                                         | Powe              | er Macintosh | model   |

|-----------------------------------------|-------------------|--------------|---------|

| System feature                          | 6100/60           | 7100/66      | 8100/80 |

| Maximum RAM capacity                    | 72 MB             | 136 MB       | 264 MB  |

| Maximum number of internal SCSI devices | 2                 | 2            | 3       |

| Room for a 1-GB internal SCSI drive     | No                | No           | Yes     |

| NuBus slots                             | 1*                | 3            | 3       |

| Maximum VRAM capacity                   | None <sup>†</sup> | 2 MB         | 4 MB    |

<sup>\*</sup> Using the optional NuBus adapter card

#### Audio and Video Features

All Power Macintosh models contain built-in support for Apple displays, using main RAM for frame buffering. This support drives monitors up to 13 inches in size at color depths up to 16 bits and monitors up to 16 inches in size at color depths up to 8 bits. The built-in display connection is described in "Built-in Interface for Video Monitors," in Chapter 3.

The Power Macintosh 7100/66 and 8100/80 models are shipped with VRAM expansion cards installed in their PDS slots. These cards provide a second monitor output in addition to the computer's built-in display support. The user can expand the VRAM capacity of these cards to drive monitors up to 21 inches at color depths up to 24 bits. The VRAM expansion cards are described in the next section.

All Power Macintosh models also feature built-in high-quality stereo sound input and output capabilities. These capabilities, which support speech recognition and synthesis as well as broadcast-quality 16-bit sound, are described in "Sound I/O," in Chapter 3.

For a description of Apple's system software support for speech recognition and synthesis, see *Macintosh Developer Note Number 5*. This book is described in "Supplementary Documents," in the preface.

Three Power Macintosh models also include the video input and output features of the Apple AV Technologies. These model are designated Power Macintosh 6100/60AV, 7100/66AV, and 8100/80AV. They contain an Apple AV card, instead of a VRAM expansion card, in their PDS slots. The Power Macintosh 7100/66AV and 8100/80AV models still accept NuBus cards; the Power Macintosh 6100/60AV cannot have a NuBus capability because its single PDS slot is occupied by the AV card. A connector on the AV card lets NuBus cards in the Power Macintosh 7100/66AV and 8100/80AV access audio and video

<sup>† 2</sup> MB with the optional AV card installed

signals directly by means of a card-to-card ribbon cable. This connector is described in "DAV Interface," in Chapter 4. AV capabilities are described in the next section; for more detailed technical information, see "AV Card," in Chapter 3.

The Power Macintosh 6100/60AV, 7100/66AV, and 8100/80AV models are shipped with built-in CD-ROM drives to support their multimedia capabilities.

Table 1-3 summarizes the VRAM capacities for second monitors in Power Macintosh computers, in addition to AudioVision display support. Table 1-3 also shows which models can accept video input and deliver video output, using the VRAM provided for the second monitor.

Table 1-3 VRAM capacities and video I/O support

|                        | VRAM      | Video I/O |

|------------------------|-----------|-----------|

| Power Macintosh model  | size (MB) | support   |

| 6100/60                | None      | No        |

| 6100/60AV              | 2         | Yes       |

| 7100/66, standard VRAM | 1         | No        |

| 7100/66, extended VRAM | 2         | No        |

| 7100/66AV              | 2         | Yes       |

| 8100/80, standard VRAM | 2         | No        |

| 8100/80, extended VRAM | 4         | No        |

| 8100/80AV              | 2         | Yes       |

|                        |           |           |

For more information about VRAM expansion, see "VRAM Expansion SIMMs," in Chapter 4. The various VRAM frame buffer sizes shown in Table 1-3 can support monitors up to 21 inches at color depths up to 24 bits, as shown in Table 1-4.

**Table 1-4** Monitors supported by various VRAM sizes

| Buffer<br>size (MB) | Monitors supported                                                       |

|---------------------|--------------------------------------------------------------------------|

| 1                   | Up to 14-inch size at up to 16 bits, up to 16-inch size at up to 8 bits  |

| 2                   | Up to 16-inch size at up to 24 bits, up to 21-inch size at up to 16 bits |

| 4                   | Up to 21-inch size at up to 24 bits                                      |

# **Apple Expansion Cards**

Apple supplies four plug-in cards for the processor-direct slot of Power Macintosh computers:

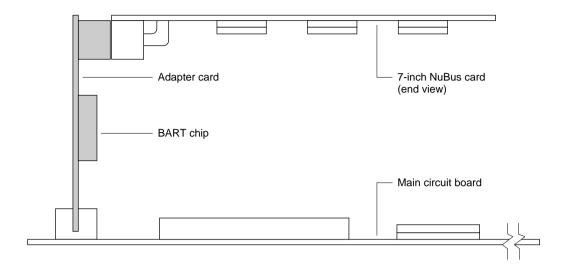

- The Power Macintosh 6100 NuBus adapter card gives the Power Macintosh 6100/60 a NuBus expansion capability. The adapter card contains the BART NuBus controller chip that is included on the main logic board of the other Power Macintosh models. It plugs into the PDS slot of the Power Macintosh 6100/60 and accepts one short (7-inch) NuBus card, which lies parallel to the main logic board. This arrangement is shown in Figure 4-1, on page 53.

- The Power Macintosh 7100 VRAM expansion card adds a second monitor output and 1 MB of 32-bit video random-access memory (VRAM) separate from system RAM. The monitor output is a DB-15 connector, described in "VRAM Expansion Cards," in Chapter 3. The user can expand the VRAM capacity to 2 MB by installing four VRAM SIMM cards. These SIMM cards are described in "VRAM Expansion SIMMs," in Chapter 4.

- The Power Macintosh 8100 VRAM expansion card acts the same as the Power Macintosh 7100 VRAM expansion card, described above, but it has 2 MB of VRAM and is expandable to 4 MB. It lets the Power Macintosh 8100/80 support 21-inch monitors to a color depth of 16 bits (using 2 MB of VRAM) or 24 bits (using 4 MB of VRAM).

- The AV card adds 2 MB of VRAM to the Power Macintosh 6100/60AV, 7100/66AV, and 8100/80AV, while extending the computer's capabilities to include the video I/O features of the Apple AV Technologies—all the video input and output features of the Macintosh Quadra 840AV and Macintosh Centris 660AV, including compatibility with NTSC, PAL, and SECAM television signals. The AV card is equipped with S-video input and output connectors as well as a DB-15 monitor connector. The user can connect the AV card to standard television equipment by means of adapter cables for composite video that are included with the computer. These video capabilities and their I/O connections are separate from the AudioVision display interface that comes with the computer.

#### **IMPORTANT**

The Power Macintosh 6100 NuBus adapter card is sold separately to users who want to add a NuBus capability to the Power Macintosh 6100/60. The VRAM expansion cards and the AV card are bundled with the specific computer models shown in Table 1-1; at present they are not available separately, and the computers are not sold without the cards. ▲

#### Note

The Power Macintosh 7100 VRAM card and the Power Macintosh 8100 VRAM card use different SIMMs to expand their VRAM capacities. For further information, see "VRAM Expansion SIMMs," in Chapter 4. ◆

# I/O Accessories

Apple offers the following I/O hardware accessories for all Power Macintosh models:

- An analog telecom adapter that plugs into the Apple GeoPort connector and communicates with a variety of telephone systems.

- An Ethernet cable adapter that plugs into the Ethernet connector.

- An adapter cable for users who want to connect a monitor that is not an AudioVision display to the built-in monitor connector. This cable has an AudioVision HDI-45 plug at one end and a DB-15 monitor socket at the other end.

- Adapter cables that plug into input and output connectors of the AV card and provide composite video, using connectors compatible with standard television equipment. These cables are included with all models that contain the AV card.

- A special microphone, optimized for speech recognition, that plugs into the audio input connector.

# Features and Capabilities

Besides standard features common to Macintosh technology, Power Macintosh computers have these new or improved capabilities:

- Direct memory access. A high-speed memory controller (HMC) and an Apple Memory-Mapped I/O Controller (AMIC) provide direct memory access (DMA) between main memory and peripheral devices. DMA permits very fast transfers of large amounts of data without burdening the main processor.

- Widely compatible video input. Models with the AV card installed can process composite or S-video inputs in NTSC, PAL, and SECAM formats from external sources such as videocams and videocassette recorders (VCRs), using standard television-type connectors. The AV card stores video information in RGB form in a frame buffer separate from main memory.

- Flexible video output. All models have a built-in capacity to support monitors up to 16-inch size. VRAM expansion cards give the Power Macintosh 7100/66 and 8100/80 a separate ability to support a second monitor up to 21-inch size. Models with the AV card installed (that is, those designated AV) can also exchange NTSC and PAL composite and S-video signals with other kinds of video equipment, including television sets and VCRs, besides driving a monitor. The AV card supports color depths up to 24 bits for graphics and 16 bits for video on a separate monitor up to 21 inches in size.

- *Improved NuBus interface*. All models use the BART NuBus controller for NuBus expansion cards. This chip is described in "Functional Units—Main Circuit Board," in Chapter 2. It supports NuBus block transfers and data bursts to and from the main processor bus. NuBus capability is optional in the Power Macintosh 6100/60 and is not available in the Power Macintosh 6100/60AV.

- Widely compatible floppy disk drive. The 1.44 MB manual-inject floppy disk drive supports both Apple's Group Code Recording (GCR) format and DOS-compatible Modified Frequency Modulation (MFM) format.

- Built-in Ethernet support. All models contain built-in circuitry for Ethernet I/O.

- *Enhanced serial ports*. Two serial ports both support RS-232 and RS-422 serial I/O protocols, as well as AppleTalk I/O over LocalTalk networks.

- Integrated telephone I/O. All models provide Apple's high-performance serial I/O capability (called GeoPort) on two serial ports, permitting connection to analog, PBX, ISDN, facsimile (fax), and data telephone lines. GeoPort supports full-duplex telephone I/O at transmission rates up to 9600 bits per second.

- Enhanced sound I/O. All models provide 16-bit digital stereo sound I/O at sample rates up to 44.1 kHz. Sound generated by the system can be mixed with CD-ROM sound in analog form.

- Large-capacity ROM. ROM chips totaling 4 MB are provided with all models. These chips contain some of the system software that is on the hard disk in other Apple computers. They are mounted on SIMM cards, so the user can replace them if an upgrade becomes available in the future.

- Expansion slots. The Power Macintosh 7100/66, 7100/66AV, 8100/80, and 8100/80AV contain three NuBus slots for long or short Macintosh expansion cards; the Power Macintosh 6100/60 accepts one short card using an optional angle adapter card. All slots carry a 32-bit data and address bus. The NuBus slots in the Power Macintosh 7100/66, 7100/66AV, 8100/80, and 8100/80AV exist in addition to the PDS slot that supports a video expansion card.

- Mass media support. All models support up to a total of seven SCSI devices. Within this limit, the user can connect several external devices to any model's SCSI port in addition to removable internal hard disk drives and CD-ROM drives.

- Fast SCSI support. The Power Macintosh 8100/80 and 8100/80 AV provide a fast SCSI interface (up to 10 MB per second) for internal SCSI devices, in addition to the standard SCSI interface.

- Software on/off power control. The Power Macintosh 7100/66 and 8100/80 provide power control service to their NuBus expansion slots, so expansion cards can turn the computer on and off.

- *Replaceable real-time clock battery.* The real-time clock and parameter RAM in all models are powered by a long-life plug-in battery.

- *Automatic SCSI termination*. Built-in circuitry provides automatic termination of the internal and external SCSI cables if no SCSI devices are connected.

Apple offers Power Macintosh computers, together with their I/O accessories and expansion cards, in all domestic and international markets for Apple computers. Units sold outside the United States are correctly localized for the regions in which they are marketed.

# Machine Identification

By using the Gestalt Manager with the identifier gestaltMachineType, an application or expansion card firmware can determine the model type of the user's system. Power Macintosh computers also set the 3 low bits of the 32-bit register at address \$5FFF FFFC to a machine identification code. Table 1-5 lists the gestalt and register values that identify each basic model of the Power Macintosh family.

Table 1-5 CPU identification

| Model                                 | Gestalt<br>value | Register<br>value |

|---------------------------------------|------------------|-------------------|

| Power Macintosh 6100/60 and 6100/60AV | \$4B             | 000               |

| Power Macintosh 7100/66 and 7100/66AV | \$70             | 010               |

| Power Macintosh 8100/80 and 8100/80AV | \$41             | 011               |

Power Macintosh computers are shipped with built-in floppy disk drives and removable internal hard disk drives. For each model, the addition of an external monitor, a keyboard, and a mouse forms a complete personal computing system.

This chapter provides a more detailed description of the memory and processing hardware common to all Power Macintosh models. For details of I/O hardware, see Chapter 3, "Input and Output Interfaces." For information about PowerPC processor operation and software, see Appendix A, "Overview of PowerPC Technology," and Appendix B, "Power Macintosh Application Development."

# Physical Forms

Power Macintosh computers are generally described in "Models and Configurations," in Chapter 1. The external dimensions of their enclosures are shown in Table 2-1.

| Table 2-1 | Evtornal | dimensions |

|-----------|----------|------------|

| Table 2-1 | External | aimensions |

|           | Power Macintosh model |                       |                       |  |

|-----------|-----------------------|-----------------------|-----------------------|--|

| Dimension | 6100/60 and 6100/60AV | 7100/66 and 7100/66AV | 8100/80 and 8100/80AV |  |

| Width     | 16.3 inches (41.4 cm) | 13.0 inches (33.0 cm) | 7.8 inches (19.7 cm)  |  |

| Depth     | 14.8 inches (37.6 cm) | 16.6 inches (42.2 cm) | 16.0 inches (40.6 cm) |  |

| Height    | 3.2 inches (8.1 cm)   | 6.0 inches (15.2 cm)  | 14.3 inches (36.2 cm) |  |

All models contain essentially the same circuitry and system components, with variations as noted in the next section.

# System Architecture

The overall data flow relations among the hardware units of Power Macintosh models 6100/60, 7100/66, and 8100/80 are summarized by the block diagram in Figure 2-1, which shows the circuitry of the Power Macintosh 8100/80. Certain parts are omitted from the main circuit board in the Power Macintosh 6100/60 and 7100/66; these parts are enclosed in dotted lines in Figure 2-1:

- In the Power Macintosh 6100/60, the BART NuBus controller and a single NuBus slot connector are mounted on a plug-in NuBus adapter card.

- In the Power Macintosh 6100/60, 6100/60AV, 7100/66, and 7100/66AV, the fast internal SCSI bus is omitted.

The units shown in Figure 2-1 are described in the next section. Components of the AV card that is bundled with the Power Macintosh 6100/60AV, 7100/66AV, and 8100/80AV are described in "Functional Units—AV Card," later in this chapter.

Squidlet BART NuBus controller 3 NuBus '90 slots PowerPC 601 microprocessor 256 KB cache PDS High-speed memory controller 4 MB ROM (HMC) DRAM array 8 MB soldered Ariel II External video DRAM array Data path 8 banks SIMM Microphone **AWAC** External speaker Apple memory-mapped Apple Desktop Bus port Cuda I/O controller (AMIC) Serial port A **Buffers** Serial port B Curio Ethernet Internal SCSI Internal floppy disk connector External SCSI Fast SCSI SWIM III Internal driver SCSI

Figure 2-1 Block diagram for Power Macintosh 8100/80

System Architecture 13

## Functional Units—Main Circuit Board

All circuitry shown in Figure 2-1 is contained on a single multilayer circuit board, which bears markings that identify each chip. Features of the major integrated circuit chips are summarized in the next sections.

#### Main Processor

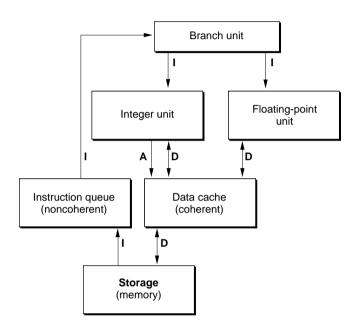

The main processor in Power Macintosh 6100/60, 7100/66, and 8100/80 computers is a PowerPC 601 microprocessor. Its operational theory is summarized in Appendix A, "Overview of PowerPC Technology." The principal features of the PowerPC 601 microprocessor include

- full RISC processing architecture

- parallel integer and floating-point processing units

- a branch manager that can usually implement branches by reloading the incoming instruction queue without using any processing time

- an internal memory management unit (MMU)

- 32 Kbit of on-chip cache memory

For complete technical details, see the Motorola *PowerPC 601 RISC Microprocessor User's Manual*. This book is listed in "Supplementary Documents," in the preface.

# Read-Only Memory

Power Macintosh computers contain 4 MB of ROM with 100-ns access time. Some of the system software that was on disk in previous Macintosh computers is in ROM in Power Macintosh models.

# Random-Access Memory

RAM for Power Macintosh computers is provided by dynamic random-access memory (DRAM) chips, of which the first 8 MB of RAM capacity is soldered to the main logic board. Users may expand RAM capacity by adding 72-pin Single Inline Memory Modules (SIMMs) in pairs. Each SIMM contains two banks of DRAM with up to 16 MB of capacity per bank. The maximum RAM capacity of each Power Macintosh model is given in Table 1-2 on page 5.

For further information about RAM SIMMs, see "RAM Expansion SIMMs," in Chapter 4. RAM addressing and RAM access details are discussed in "Memory Management," later in this chapter.

## Cache Memory

The PowerPC 601 microprocessor maintains a 32-Kbit internal first-level cache. For details of its organization and operation, see the Motorola *PowerPC 601 RISC Microprocessor User's Manual*. This book is listed in "Supplementary Documents," in the preface.

All Power Macintosh models accept an external second-level cache on a SIMM. The second-level cache size may range from 128 KB to 256 KB. The Power Macintosh 8100/80 is shipped with all 256 KB already installed; users of other models in the Power Macintosh family can install a second-level cache by plugging a SIMM into a 160-pin connector on the main logic board. The high-speed memory controller (HMC) interrogates two pins of this connector during system startup, to determine the size of the memory on the SIMM. If no SIMM is installed, pull-up resistors on these pins cause the HMC to disable all external cache operations. The HMC is described in the next section.

For pin assignments and mechanical details of the cache SIMM, see "Cache Expansion SIMMs," in Chapter 4.

## **High-Speed Memory Controller**

The **high-speed memory controller (HMC)** is an ASIC chip that controls all memory operations in Power Macintosh computers. The HMC has the following features that support data transfers to and from the PowerPC 601 processor:

- support for all basic transfer protocols, including all single-cycle accesses

- support for four-cycle 32-byte cache accesses

- translation of misaligned read actions into double-word read actions

- implementation of address-only transactions

- bus arbitration (of the address bus only) as described in "CPU Bus Arbitration," later in this chapter.

The HMC does not support the following features:

- pipelining of memory bus transactions

- cache snooping

- recovery from transfer error acknowledge signals

- little-endian transfer mode (see "Data Organization," in Appendix A)

# Apple Memory-Mapped I/O Controller

The **Apple Memory-Mapped I/O Controller (AMIC)** is a 160-pin gate array chip that performs most I/O logic and control for Power Macintosh computers. It supports the following functions:

- handling interrupts received through Versatile Interface Adapter (VIA) channels

- DMA for Ethernet I/O

- DMA for the SWIM III floppy disk drive controller

- DMA for the Serial Communications Controller (SCC) I/O

- DMA for Small Computer System Interface (SCSI) device support

- DMA for sound I/O

- monitor support

The AMIC does not support the extended transfer protocols of the PowerPC 601 processor; using these protocols will cause a transfer error exception.

## Data Path Chips

Two data path (DP) chips provide buffering between I/O and DRAM memory accesses and the cached CPU bus. They perform the following functions:

- route byte lanes between 8-bit and 16-bit I/O processes and the 64-bit CPU bus

- provide first-in, first-out (FIFO) buffering for video monitor data, which is fetched from RAM as eight-cycle bursts

- supply the Ariel II video chip with appropriate timing signals for video monitor data The Ariel II video chip is described in the next section.

## Ariel II Video Chip

The **Ariel II** video chip provides a color lookup table (CLUT) and digital-to-analog converter (DAC) for driving an AudioVision monitor. For information about monitors compatible with Power Macintosh computers, see "Built-in Interface for Video Monitors," in Chapter 3.

# SWIM III Floppy Disk Drive Controller

The **SWIM III** floppy disk drive controller is an extension of the SWIM II circuitry used in models such as the Macintosh Quadra 800 and Macintosh Centris 650. It includes the following new features:

- support for DMA data transfers, which minimize use of the main processor

- no requirement that interrupts be disabled during floppy disk accesses

- support for GCR and MFM formats on 1.44 MB disks

- compatibility with the manual-inject floppy disk drive

Floppy disk drives designed to be compatible with the New Age controller used in the Macintosh Quadra 840AV and Macintosh Centris 660AV computers can easily be adapted for compatibility with the SWIM III controller.

## Curio I/O Chip

The **Curio** is a multipurpose I/O chip that contains a Media Access Controller for Ethernet (MACE), a SCSI controller, and a Serial Communications Controller (SCC).

The SCC section of the Curio includes 8-byte FIFO buffers for both transmit and receive data streams.

Curio functions are discussed in "External Device Interfaces," in Chapter 3.

## Cuda Microcontroller Chip

The **Cuda** is a microcontroller chip. It

- turns system power on and off

- manages system resets from various commands

- maintains parameter RAM

- manages the Apple Desktop Bus (ADB)

- manages the real-time clock

- lets an external signal from either Apple GeoPort serial port control system power

The ADB is discussed in more detail in "Apple Desktop Bus," in Chapter 3; Apple GeoPort is discussed in "Serial Ports," in the same chapter.

# **AWAC Sound Chip**

The **audio waveform amplifier and converter (AWAC)** is a 44-pin chip that combines a waveform amplifier with a 16-bit digital sound encoder and decoder (codec). It conforms to the IT&T *ASCO 2300 Audio-Stereo Codec Specification* (listed in "Supplementary Documents," in the preface) and furnishes high-quality sound I/O for Power Macintosh computers. For details of AWAC operation, see "Sound I/O," in Chapter 3.

#### BART NuBus Controller

The **BART NuBus controller** chip provides the data gateway between NuBus and the CPU bus. It acts as a CPU bus master, transferring one-cycle or four-cycle transactions. It is compliant with the IEEE Standard 1196 listed in "Supplementary Documents," in the preface. For further information about NuBus in Power Macintosh computers, see "NuBus Interface," in Chapter 4, and the Macintosh Hardware Technical Notes.

# Squidlet Chip

**Squidlet** is a 28-pin chip that provides a set of synchronized system clocks for Power Macintosh computers. Clock frequencies are listed in "System Clocks," later in this chapter.

## Functional Units—AV Card

The AV card, described in "Apple Expansion Cards," in Chapter 1, is bundled with the Power Macintosh 6100/60 AV, 7100/66 AV, and 8100/80 AV. Features of the major chips on the AV card are summarized in the next sections. For details of their operation, see "AV Card," in Chapter 3.

### Cyclone Integrated Video Interfaces Controller

The **Cyclone Integrated Video Interfaces Controller (CIVIC)**, used in the AV card, is a CMOS chip in a 144-pin package. The CIVIC

- manages from 1 MB to 4 MB of video RAM (VRAM)

- controls data transfers between VRAM and the SAA7194 chip and between VRAM and the Sebastian video color palette chip (both chips are described later in this chapter)

- provides 32-bit or 64-bit data paths between VRAM and the main processor; supports data bursts from the main processor in all transfer modes

- controls convolution of graphics data for line-interlaced displays

- provides NTSC and PAL timing signals

- generates vertical blanking and video-in interrupt signals

# Sebastian Chip

The **Sebastian** chip is a video color palette and video digital-to-analog converter (DAC) in a 100-pin CMOS configuration, used in the AV card. The Sebastian

- accepts digital data up to 64 bits wide, either as one 64-bit port or as one or two 32-bit ports

- lets one 32-bit port handle digital video while the other processes graphics (including QuickTime), using the same or different color lookup tables

- supports mixing video with still graphics, even with different color depths

- supports both Truecolor and pseudocolor with alpha color lookup

- supports a transparency effect when blending video with still graphics under the control of alpha channel bits at 1 to 8 bits per pixel

- uses a convolution filter to minimize flicker in line-interlaced displays

- supports displays with dot clocks up to 100 MHz

#### SAA7194 Decoder

The SAA7194 is a Philips CMOS chip that decodes the color information in NTSC, PAL, and SECAM video formats using a clock synchronized to their line frequency. It is used in the AV card. The SAA7194 also

- performs input video window scaling with horizontal and vertical filtering

- produces 16-bit 1:5:5:5 RGB, 8-bit grayscale, or YUV 4:2:2 output

For details of SAA7194 operation, see "AV Card," in Chapter 3.

## Mickey Encoder

The **Mickey** is a composite video encoder in a 28-pin advanced bipolar CMOS chip. It is used in the AV card. The Mickey

- accepts analog RGB video signals from the Sebastian video color palette chip

- encodes to NTSC or PAL format

- produces S-video, composite, or RGB video outputs

# System Clocks

The Power Macintosh circuitry is driven by several different clocks running at different frequencies. Clocks that run at different rates in different models include the system clock, which is controlled by an oscillator and drives the PowerPC processor, and the CPU bus clock, which is controlled by the system clock. The frequencies of these clocks are listed in Table 2-2.

Table 2-2 Model-specific clocks

| Power Macintosh models | System clock<br>frequency (MHz) | CPU bus clock frequency (MHz) |

|------------------------|---------------------------------|-------------------------------|

| 6100/60 and 6100/60AV  | 60.0000                         | 30.0000                       |

| 7100/66 and 7100/66AV  | 66.0000                         | 33.0000                       |

| 8100/80 and 8100/80AV  | 80.0000                         | 40.0000                       |

System Clocks 19

Clocks that run at the same rate in the Power Macintosh 6100/60, 6100/60AV, 7100/66AV, 8100/80, and 8100/80AV are listed in Table 2-3.

Table 2-3

Fixed-rate system clocks

| Name     | Frequency<br>(MHz) | Source     | Use                                  |

|----------|--------------------|------------|--------------------------------------|

| I/O      | 31.3344            | Oscillator | I/O components, 12-inch monitor, SCC |

| VGA      | 25.1570            | Oscillator | VGA monitor                          |

| Dot      | 57.2832            | Oscillator | 16-inch monitor                      |

| Ethernet | 20.0000            | Oscillator | Ethernet, SCSI                       |

| Cuda     | 0.0320             | Crystal    | Cuda real-time clock                 |

| Sound    | 44.1584            | Oscillator | Sound sample rate                    |

# **CPU Bus**

The CPU bus is the standard 64-bit nonpipelined bus used by the PowerPC 601 processor. Expansion cards can connect to the CPU bus through the processor-direct slot (PDS) connector, described in "PDS Expansion Cards for the Power Macintosh 6100/60," in Chapter 4.

### **CPU Bus Arbitration**

The HMC performs arbitration of the address part of the CPU bus in the order shown in Table 2-4, with the processor having default access. Access to the data part of the CPU bus is dependent on access to the address part.

Table 2-4 CPU bus arbitration order

| Priority | Requestor            |

|----------|----------------------|

| Highest  | DRAM refresh         |

|          | Video refresh        |

|          | I/O DMA for SWIM III |

|          | I/O DMA for AWAC     |

|          | I/O DMA for SCSI     |

|          | I/O DMA for SCC      |

|          | Expansion card       |

| Lowest   | Main processor       |

|          |                      |

An expansion card can assert control of the CPU bus, subject to these design considerations:

- The requesting card must verify that the bus is free by checking signal ABB (pin 125).

- Original access to the bus is delayed by a latency period of one CPU clock cycle.

- Only basic processor cycles and cache line operations are recognized.

- A slave expansion card must decode its own memory space and must ensure that it does not interfere with the computer's main memory usage.

- Higher-priority bus grants may interfere with a card's access to the bus; in particular, video refresh actions may sometimes absorb much of the bus capacity.

#### **Address Errors**

The main processor's memory management unit (MMU) normally maps only address spaces that are decoded in hardware. Attempts to access undecoded addresses result in an MMU error, which is recoverable.

If an attempt is made to access an address that is mapped by the MMU but not decoded in hardware, the AMIC chip asserts an error signal after  $40~\mu s$ . This error condition is not generally recoverable; it forces the user to restart the computer.

# Memory Management

All memory operations are controlled by the HMC chip, described in "High-Speed Memory Controller," earlier in this chapter.

# **Memory Organization**

Memory in Power Macintosh computers is organized in three levels:

- internal cache memory in the main processor

- external second-level cache memory

- DRAM memory

The internal cache memory capacity is 32 Kbits. The user can expand external secondary cache capacity up to 256 KB. The limits to RAM capacity for various models are given in Table 1-2 on page 5.

Details of physical memory space access are given in the next section.

### **Physical Memory Allocations**

A single 32-bit physical memory space contains the memory allocations shown in Table 2-5. Virtual memory operations are supported by the internal memory management unit of the PowerPC 601 microprocessor. Logical memory mapping is established by the system software.

**Table 2-5** Physical memory allocations

| Used for     |

|--------------|

| RAM          |

| RAM aliases  |

| ROM          |

| I/O          |

| Not assigned |

| ROM alias    |

|              |

#### RAM Access

All Power Macintosh models use 80-ns dynamic RAM chips. The RAM system supports the PowerPC 601 four-cycle bus transaction and all PowerPC 601 single-cycle bus transactions. It does not support any of the PowerPC 601 extended protocol bus transactions.

#### Note

Transactions where the CPU bus is master have the lowest priority among RAM access requests. For further information, see "CPU Bus Arbitration," earlier in this chapter. ◆

DRAM refresh takes place as a CAS before RAS memory cycle every 15.6  $\mu$ sec. This cycle does not affect RAM timing for data accesses.

# Interrupt Handling

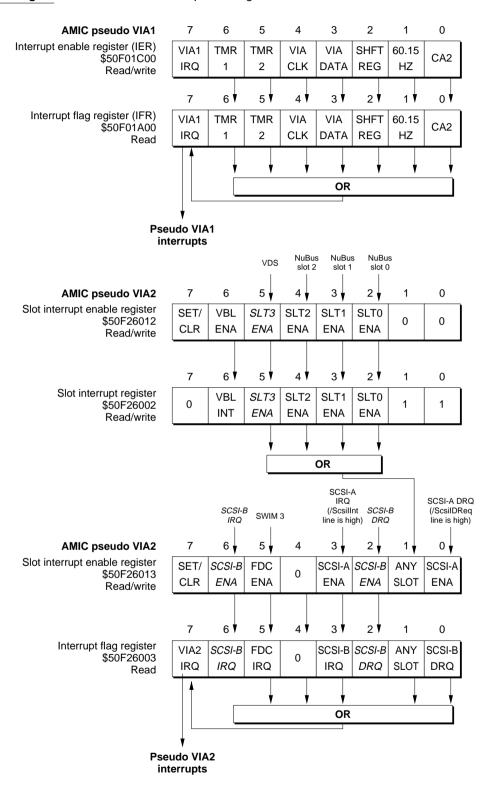

Traditional Macintosh software is designed for the seven-level interrupt structure of the Motorola MC68000 family of processors. The PowerPC 601 processor, however, has only a single interrupt line and service routine. The AMIC chip resolves this difference by emulating the MC68000 interrupt structure and accepting interrupts through the traditional VIA channels. The process of handling VIA1 and VIA2 interrupts in the Power Macintosh 7100/66, 7100/66AV, 8100/80, and 8100/80AV is diagrammed in Figure 2-2. Elements not present in the Power Macintosh 6100/60 and 6100/60AV are labeled in *italics*.

For further information about interrupt handling through the VIA channels, see *Inside Macintosh: Processes*.

Hardware Overview

Figure 2-2 Emulated interrupt handling

Interrupt Handling 23

Power Macintosh computers are offered with two levels of I/O capability:

- Models without an AV designation after the model name provide the I/O features that are currently standard for Macintosh Quadra computers: ADB, GeoPort, SCSI, a floppy disk drive, built-in Ethernet, high-quality 16-bit stereo sound, and various levels of monitor support up to 21 inches, depending on the model.

- Models with an AV designation (the Power Macintosh 6100/60AV, 7100/66AV, and 8100/80AV) provide the full range of Apple AV Technologies in addition to the standard I/O features; they add video input and output, as well as support for 21-inch monitors.

This chapter provides details of the Power Macintosh I/O hardware and interfaces. For a list of Power Macintosh configurations, see Table 1-1 on page 4.

## **External Device Interfaces**

This section discusses the interfaces between Power Macintosh computers and external devices through

- the ADB, which supports keyboards, mouse devices, trackballs, and other user-input devices

- an Ethernet port for wide area network access

- two serial ports for printers, modems, AppleTalk, and other serial I/O devices

- a SCSI connection for devices such as hard disk drives

- an interface to the Apple SuperDrive floppy disk drive

For video interface information, see "Built-in Interface for Video Monitors," later in this chapter. For sound interface information, see "Sound I/O," later in this chapter.

## Apple Desktop Bus

The Apple Desktop Bus (ADB) is an asynchronous serial communication bus used to connect relatively slow user-input devices to Macintosh computers. Its software characteristics are described in *Inside Macintosh: Operating System Utilities*. One ADB connector is located on the back panel of Power Macintosh computers. It is a 4-pin mini-DIN socket, as shown in Figure 3-1.

Figure 3-1 ADB socket

The ADB pin assignments are shown in Table 3-1.

Table 3-1 ADB pin assignments

| Pin | Description                                                                           |

|-----|---------------------------------------------------------------------------------------|

| 1   | Data; grounded by an open collector or pulled to +5 V through 470 $\Omega$            |

| 2   | Power on, fed by +5 V through 100 k $\Omega$ ; connect to pin 4 to turn on the system |

| 3   | +5 V at 500 mA maximum drain; protected by a 1.25-A circuit breaker                   |

| 4   | Ground return                                                                         |

## **Ethernet Port**

All models of Power Macintosh computers contain built-in support for Ethernet. The user can plug a drop-box cable (available from Apple or from third-party vendors) into a standard Ethernet connector on the computer.

The Ethernet port pin assignments are shown in Table 3-2.

Table 3-2

Ethernet port pin assignments

| Pin | Description | Pin | Description   |

|-----|-------------|-----|---------------|

| 1   | +5 V        | 8   | +5 V          |

| 2   | DI+         | 9   | DO+           |

| 3   | DI–         | 10  | DO-           |

| 4   | Ground      | 11  | Ground        |

| 5   | CI+         | 12  | No connection |

| 6   | CI-         | 13  | No connection |

| 7   | +5 V        | 14  | +5 V          |

## **Serial Ports**

The back panel on all models of Power Macintosh computers contains two I/O ports for serial telecommunications data. Both sockets accept 9-pin plugs, as shown in Figure 3-2.

Figure 3-2 Serial port connector

Either port can be independently programmed for asynchronous or synchronous communication formats up to 9600 baud, including AppleTalk and the full range of Apple GeoPort protocols. Through these ports, the computer can communicate with a variety of ISDN and other telephone transmission facilities by using external pods.

Table 3-3 gives the pin assignments for both serial ports.

Table 3-3

Serial port pin assignments

| Pin | Name                  | Function                                    |

|-----|-----------------------|---------------------------------------------|

| 1   | SCLK <sub>out</sub>   | Reset pod or get pod attention              |

| 2   | $Sync_{in}/SCLK_{in}$ | Serial clock from pod (up to 920 Kbit/sec.) |

| 3   | TxD-                  | Transmit –                                  |

| 4   | Gnd/shield            | Ground                                      |

| 5   | RxD-                  | Receive –                                   |

| 6   | TxD+                  | Transmit +                                  |

| 7   | Wakeup/TxHS           | Wake up CPU or do DMA handshake             |

| 8   | RxD+                  | Receive +                                   |

| 9   | +5 V                  | Power to pod (350 mA maximum)               |

## SCSI Connection

The SCSI interface in Power Macintosh computers exists in two forms: an internal 50-pin ribbon connector for internal devices and an external DB-25 connector for external devices.

Power Macintosh computers contain space for the numbers of internal SCSI devices shown in Table 3-4. All models accept up to a total of seven internal and external SCSI devices combined.

Table 3-4 Spaces for internal SCSI devices

| Power Macintosh model | CD-ROM<br>drive | Hard disk drives<br>(up to 500 MB each) | Hard disk drives<br>(up to 1 GB each) |