# Macintosh PowerBook 140 and Macintosh PowerBook 170

Developer Note

**Developer Note**

Developer Technical Publications © Apple Computer, Inc. 1991

APPLE COMPUTER, INC.

© 1991, Apple Computer, Inc.

All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, mechanical, electronic, photocopying, recording, or otherwise, without prior written permission of Apple Computer, Inc. Printed in the United States of America.

The Apple logo is a registered trademark of Apple Computer, Inc. Use of the "keyboard" Apple logo (Option-Shift-K) for commercial purposes without the prior written consent of Apple may constitute trademark infringement and unfair competition in violation of federal and state laws.

Apple Computer, Inc. 20525 Mariani Avenue Cupertino, CA 95014-6299 408-996-1010

Apple, the Apple logo, APDA, AppleLink, AppleTalk, LaserWriter, Macintosh, and SANE are trademarks of Apple Computer, Inc., registered in the United States and other countries.

Apple DeskTop Bus, Balloon Help, PowerBook, QuickDraw, and SuperDrive are trademarks of Apple Computer, Inc.

Classic is a registered trademark, licensed to Apple Computer, Inc.

Adobe Illustrator and PostScript are registered trademarks of Adobe Systems Incorporated.

ITC Garamond and ITC Zapf Dingbats are registered trademarks of International Typeface Corporation.

MacDraw is a registered trademark of Claris Corporation.

Microsoft is a registered trademark of Microsoft Corporation.

#### LIMITED WARRANTY ON MEDIA AND REPLACEMENT

If you discover physical defects in the manual or in the media on which a software product is distributed, APDA will replace the media or manual at no charge to you provided you return the item to be replaced with proof of purchase to APDA.

ALL IMPLIED

WARRANTIES ON THIS

MANUAL, INCLUDING

IMPLIED WARRANTIES

OF MERCHANTABILITY

AND FITNESS FOR A

PARTICULAR PURPOSE,

ARE LIMITED IN

DURATION TO NINETY

(90) DAYS FROM THE

DATE OF THE ORIGINAL

RETAIL PURCHASE OF

THIS PRODUCT.

Even though Apple has reviewed this manual, APPLE MAKES NO **WARRANTY OR** REPRESENTATION, EITHER EXPRESS OR IMPLIED, WITH RESPECT TO THIS MANUAL, ITS QUALITY, ACCURACY, MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE. AS A RESULT, THIS MANUAL IS SOLD "AS IS," AND YOU, THE PURCHASER, ARE ASSUMING THE ENTIRE RISK AS TO ITS QUALITY AND ACCURACY.

IN NO EVENT WILL APPLE BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES RESULTING FROM ANY DEFECT OR INACCURACY IN THIS MANUAL, even if advised of the possibility of such damages.

THE WARRANTY AND REMEDIES SET FORTH ABOVE ARE EXCLUSIVE AND IN LIEU OF ALL OTHERS, ORAL OR WRITTEN, EXPRESS OR IMPLIED. No Apple dealer, agent, or employee is authorized to make any modification, extension, or addition to this warranty.

Some states do not allow the exclusion or limitation of implied warranties or liability for incidental or consequential damages, so the above limitation or exclusion may not apply to you. This warranty gives you specific legal rights, and you may also have other rights which vary from state to state.

# **Contents**

```

Figures and Tables / v

Preface / vii

About this note / vii

Supplemental reference documents / vii

The Hardware / 1

Introduction / 2

Features / 2

Design architecture / 3

Machine identification / 4

Compatibility issues / 6

Floppy disks / 6

External SCSI connector / 6

SCSI and SCC implementation / 6

Sound input/output hardware / 7

On-board mathematics coprocessor (FPU) / 7

Hardware overview / 8

Main processor / 8

Memory mapping / 8

Custom integrated circuits / 11

CPU GLU / 11

DDC (Display Driver Chip) / 11

Miscellaneous GLU / 11

ROM interface / 12

RAM interface / 12

RAM expansion / 13

RAM expansion connector signals / 15

RAM expansion card design guide / 17

Floppy disk interface / 19

SCC and SCSI interfaces / 20

SCC / 20

SCSI / 21

Internal hard disk drive / 23

```

```

Hard disk drive design considerations / 23

Power requirements for 40 MB hard disk drive / 23

Power requirements for 20 MB hard disk drive / 24

Sound interface / 26

VIA interface / 27

Video interface / 27

Flat-panel display and backlighting / 27

Power Manager / 28

Power states / 28

Shutdown feature / 29

Power cycling / 30

Guidelines for developing application software for a

power-cycling environment / 31

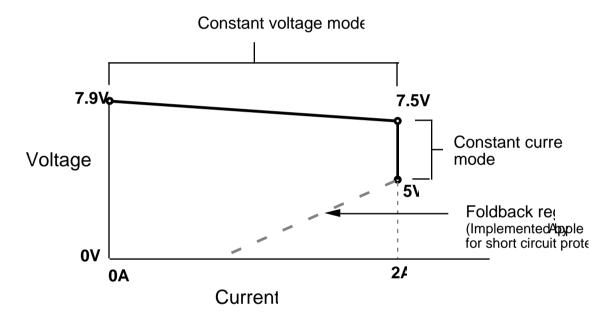

A/C power adapter / 31

Modem interface / 32

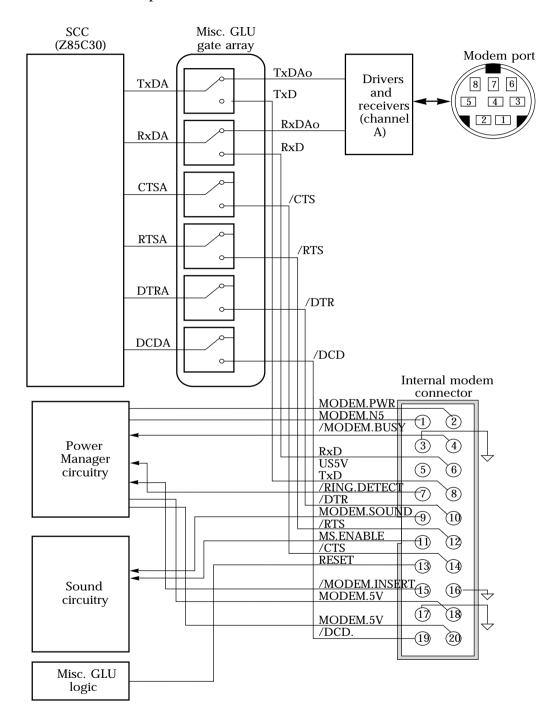

Modem card electrical interface / 32

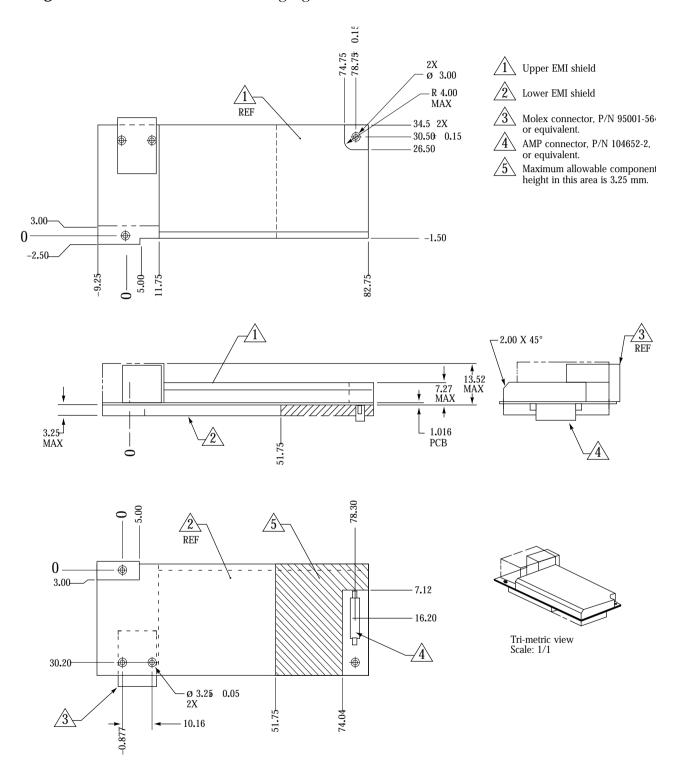

Modem card hardware interface / 34

Physical design guide for a modem card / 34

Modem power-control interface / 37

Modem operation / 38

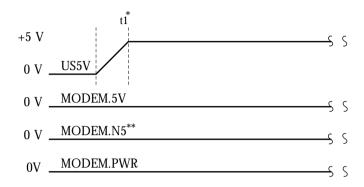

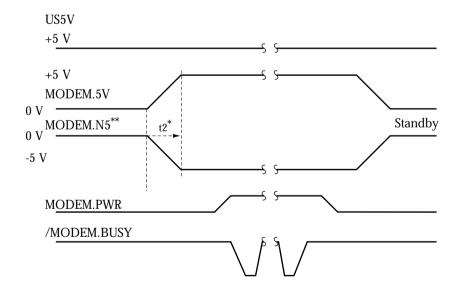

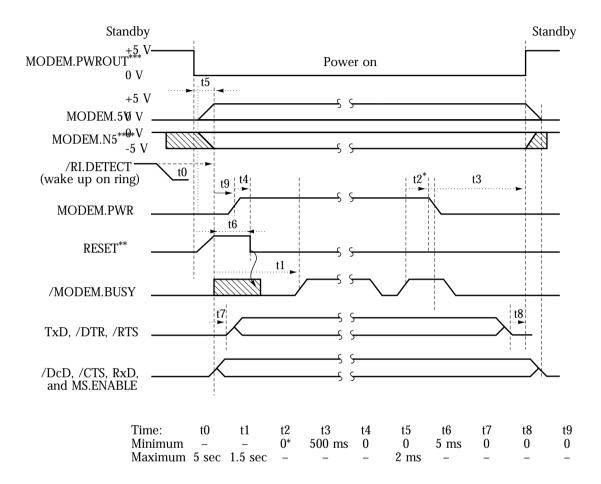

Power-up/power-down timing / 38

Ring detection / 41

Modem card power requirements / 41

Telephone line electrical interface / 41

Modem specifications / 42

Compatibility and modulation / 42

Transmit carrier frequencies / 42

Guard tone frequencies and transmit levels (CCITT

only) / 43

Answer tone frequency / 43

Received signal frequency tolerance / 43

Calling tone / 43

Keyboard overview / 43

Keyboard layouts / 43

Caps Lock modification / 45

The Software / 47

The ROM / 48

```

System software / 48

# **Figures and Tables**

1

| The Hardw    | rare / 1                                                                               |

|--------------|----------------------------------------------------------------------------------------|

|              | Block diagram of the Macintosh PowerBook<br>40 and Macintosh PowerBook 170 computers / |

| _            | 32-bit memory and detailed I/O map / 9                                                 |

|              | 32-bit and 24-bit memory maps / 10                                                     |

|              | Location of modem and RAM expansion                                                    |

| rigule 1-4   | onnectors / 14                                                                         |

|              | ·                                                                                      |

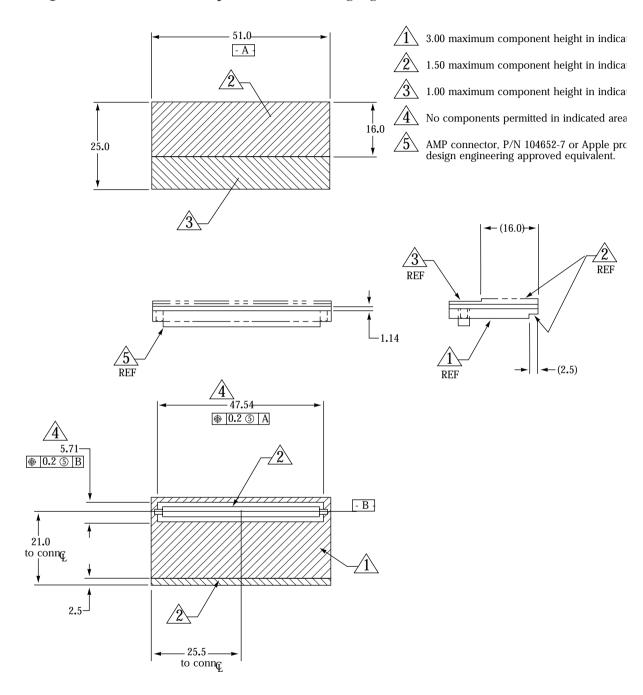

|              | RAM expansion card design guide / 18                                                   |

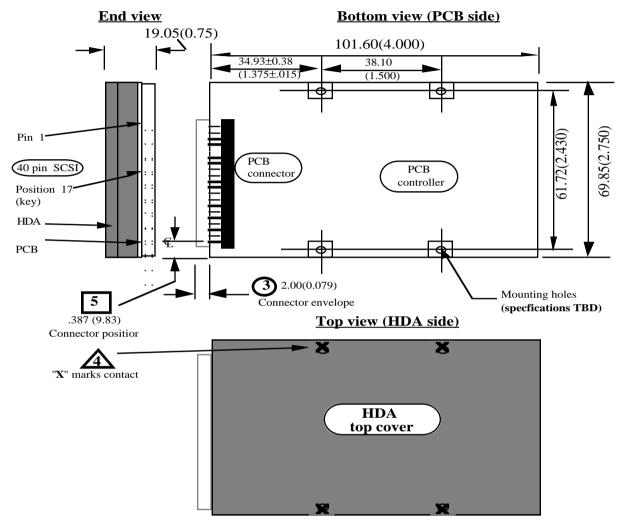

| 0            | Envelope requirement for the 2.5-inch hard isk                                         |

|              |                                                                                        |

|              | rive / 25                                                                              |

| 0            | Typical A/C power adapter operating range /                                            |

| 32           |                                                                                        |

|              | Interface between the modem card and the                                               |

|              | omputer / 35                                                                           |

|              | Modem card design guide / 36                                                           |

| Figure 1-10  |                                                                                        |

|              | ming                                                                                   |

|              | iagram / 39                                                                            |

|              | Modem warm-start timing diagram / 39                                                   |

|              | Complete power-up/power-down                                                           |

|              | equence timing                                                                         |

|              | iagram / 40                                                                            |

| Figure 1-13  | U.S. and ISO keyboard layouts / 44                                                     |

| Figure 1-14  | Caps Lock "down" / 45                                                                  |

| Figure 1-15  | Caps Lock "up" / 45                                                                    |

| Table 1-1 R  | AM expansion connector signals / 15                                                    |

|              | inout for internal floppy disk connector / 19                                          |

| Table 1-3 Se | erial port pinouts / 20                                                                |

|              | inouts for internal and external HDI-30 SCSI                                           |

| CO           | onnectors / 22                                                                         |

|              | ower states / 29                                                                       |

|              | Modem connector signals / 33                                                           |

# **Preface**

#### About this note

This developer note describes the Macintosh PowerBook 140 and Macintosh PowerBook 170 computers and emphasizes features that are new and different from those of the Macintosh Portable and the Macintosh PowerBook 100 computers. This note assumes that you are already familiar with both the capabilities and programming requirements of Apple Macintosh computers, in particular the Macintosh Portable computer. If you are unfamiliar with Macintosh computers or would simply like more technical information on the hardware, you may want to obtain copies of related technical manuals. For information on how to obtain these manuals, see the following section.

## For more information

To supplement the information in this document, you might wish to obtain related documentation such as *Guide to the Macintosh Family Hardware*, second edition; *Designing Cards and Drivers for the Macintosh Family*, second edition (third edition will soon be available), and *Inside Macintosh*, Volumes I through VI. Copies of these manuals are available through APDA (Apple Programmers and Developers Association). APDA offers convenient worldwide access to over 300 development tools, resources, and training products and to information for anyone interested in developing applications on Apple platforms. Customers receive the quarterly *APDA Tools Catalog*, featuring the most current versions of Apple development tools and the most popular third-party development tools. Ordering is easy; there are no membership fees, and application forms are not required for most of our

| products. APDA site licensing. | offers convenient | t payment and | shipping options, | including |

|--------------------------------|-------------------|---------------|-------------------|-----------|

|                                |                   |               |                   |           |

|                                |                   |               |                   |           |

|                                |                   |               |                   |           |

|                                |                   |               |                   |           |

|                                |                   |               |                   |           |

|                                |                   |               |                   |           |

|                                |                   |               |                   |           |

|                                |                   |               |                   |           |

|                                |                   |               |                   |           |

|                                |                   |               |                   |           |

|                                |                   |               |                   |           |

|                                |                   |               |                   |           |

|                                |                   |               |                   |           |

|                                |                   |               |                   |           |

To order products or get additional information, contact

APDA Apple Computer, Inc. 20525 Mariani Avenue, M/S 33-G Cupertino, CA 95014-6299

800-282-2732 (United States) 800-637-0029 (Canada) 408-562-3910 (International)

Fax: 1-408-562-3971 Telex: 171-576

AppleLink address: APDA

# Chapter 1 The Hardware

This chapter describes the major features of the Macintosh PowerBook 140 and Macintosh PowerBook 170 computers, and emphasizes the similarities and differences between these computers, the original Macintosh Portable computer, and other members of the Macintosh computer family.

#### Introduction

The Macintosh PowerBook 140 and Macintosh PowerBook 170 computers are new laptop, battery-operated, portable Macintosh computers weighing 6.8 pounds. They are smaller and lighter than the current Macintosh Portable, offer improved state-of-the-art CPU performance, are designed to be extremely rugged and portable, and should appeal to anyone wishing to use a Macintosh computer away from its usual environment (office, classroom, laboratory, and so on).

The Macintosh PowerBook 140 has a 68030 microprocessor running at 16 MHz, a backlit Film SuperTwist Nematic (FSTN) display, and a built-in 20 MB hard disk. The more powerful Macintosh PowerBook 170 has a 68030 microprocessor running at 25 MHz, a 68882 FPU (floating-point unit), a backlit active matrix display, and a built-in 40 MB hard disk. The Macintosh PowerBook 140 does not include a 68882 FPU. To enhance the overall capabilities of these portable computers, expansion slots (connectors) are provided for RAM cards and modem cards.

#### **Features**

This section lists the major features of the Macintosh PowerBook 140 and the Macintosh PowerBook 170 portable computers.

- Microprocessor: 68030 running at 25 MHz (Macintosh PowerBook 170) and 16 MHz (Macintosh PowerBook 140).

- Coprocessor: 68882 FPU (not available on Macintosh PowerBook 140).

- Read-only memory (ROM): 1 MB.

- Random-access memory (RAM): 2 MB of pseudostatic RAM (PSRAM) on main logic board; in addition, PowerBook 170 includes 2 MB RAM expansion card.

- RAM expansion: RAM expansion card that allows RAM expansion in increments of 2 MB, 4 MB, or 6 MB.

- Video display: Macintosh PowerBook 170 has a flat-panel, transreflective active matrix LCD (liquid crystal display); Macintosh PowerBook 140 has a flat-panel, transmissive mode, FSTN LCD. Both displays are 640 x 400 pixels, with on-demand CCFL (cold cathode fluorescent lamp) backlighting.

- Floppy disk: one internal 20-pin floppy disk connector and one internal 1.4 MB 19-mm Apple SuperDrive with Super Woz Integrated Machine (SWIM) interface. Drive does not have automatic inject feature.

- Hard disk: one 30-pin flex cable with HDI (high-density interface) 30-pin SCSI (Small Computer System Interface) connector for internal hard disk drive. The Macintosh PowerBook 170 has one internal 40 MB, 2.5-inch SCSI hard disk drive; the Macintosh PowerBook 140 has one internal 20 MB, 2.5-inch SCSI hard disk drive.

- I/O (input/output): one HDI-30 SCSI connector for an external device, one mini-DIN, 4-pin Apple Desktop Bus (ADB) port, two mini-DIN 8-pin serial ports, and audio input and stereo output jacks; no connector for an external floppy disk drive.

- Sound: enhanced Apple Sound Chip (ASC) that supports stereo sound out.

- Keyboard: built-in 3.0-mm travel keyboard with centered pointing device (30-mm trackball); no built-in keypad option.

- Modem: internal 20-pin connector for 2400-baud modem card with send fax (modem is standard in Macintosh PowerBook 170, optional in Macintosh PowerBook 140).

- Battery: 2.5 ampere-hour NiCad rechargeable battery; backup provided by 3-V rechargable lithium battery.

- Power jack: external jack that provides the interface for the external wall-mounted recharger/power adapter.

- Weight: 6.8 pounds.

- Size: 11.3 inches wide, 9.3 inches long, and 2.25 inches high.

## Design architecture

These new portable computers include many of the Macintosh Portable computer's architectural features such as power management, SWIM, and Versatile Interface Adapter (VIA) functions. The powerful 68030 microprocessor replaces the 68HC000 microprocessor used in the Macintosh Portable. A Combo chip, identical to that used in the Macintosh IIsi and the Macintosh LC computers, combines the functions of SCSI and SCC (Serial Communications Controller). Sound input and output are implemented using an enhanced Apple Sound Chip, low-power discrete audio output circuitry, and the Digitally Filtered Audio Chip (DFAC).

One of the primary considerations in the design was power conservation. A unique power cycling feature turns off the 68030 processor (and the 68882 coprocessor on the Macintosh PowerBook 170) when they are not in use, thus drastically reducing power consumption. PSRAM, the same as used in the backlit version of the Macintosh Portable, replaces the SRAM (static RAM) used in the original version of Macintosh Portable and has the advantage of providing lower sleep current at reduced cost.

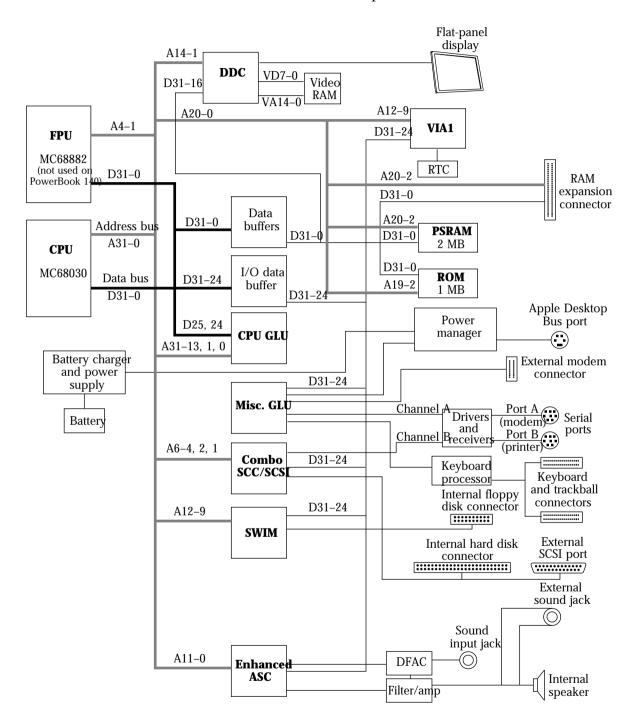

The design includes three new custom integrated circuits (ICs): CPU GLU (General Logic Unit), Miscellaneous GLU, and the DDC (Display Driver Chip). The CPU GLU serves as the interface to the circuits that communicate with the main processor, the Miscellaneous GLU provides the random logic functions for circuits that communicate with the Power Manager, and the DDC provides access to a separate SRAM to support the flat-panel display. Figure 1-1 is a block diagram showing the relationships of the major components of the computers.

# Machine identification

By using the Gestalt Manager (the successor to SysEnvirons), you can determine whether your application is running on a Macintosh PowerBook 140, a Macintosh PowerBook 170, or another Macintosh model. You should first check for the appropriate machine selector code (21 for both the Macintosh PowerBook 140 and the Macintosh PowerBook 170). Next check for the presence or absence of an FPU, as explained in "On-board Mathematics Coprocessor (FPU)." later in this chapter. If the routine returns a selector code of 21 and also indicates that an FPU is present, then your application is running on a Macintosh PowerBook 170. A selector code of 21 together with the absence of an FPU identifies the machine as a Macintosh PowerBook 140. A selector code other than 21 indicates some other Macintosh model.

# • **Figure 1-1** Block diagram of the Macintosh PowerBook 140 and Macintosh PowerBook 170 computers

# Compatibility issues

Although the architecture of the new portable computers is based partially on that of the original Macintosh Portable, it also incorporates many new features, resulting in some possible hardware and software compatibility issues. The rest of this section describes those new features and related compatibility issues.

### Floppy disks

The Macintosh PowerBook 140 and Macintosh PowerBook 170 computers have only one built-in 1.4 MB SuperDrive and do not have a connector for an external floppy disk drive.

#### **External SCSI connector**

An HDI-30 connector provides the SCSI interface for external devices. This connector is smaller and has a different pinout than the DB-25 SCSI connector used on previous Macintosh computers. Electrical information is provided in the section "SCC and SCSI Interfaces" later in this chapter.

# SCSI and SCC implementation

The Combo chip combines the functions of SCSI and SCC and is described in the section "SCC and SCSI Interfaces" later in this chapter. Although this chip is software compatible with the previous implementation of these functions, your applications may be inoperable if they attempt to access the hardware directly.

An application should use normal communications calls to talk to the serial driver; it should never attempt to get direct access to the SCC hardware. The serial chip is turned off when not in use; if your application makes normal serial communications calls, the serial driver knows how to turn the serial chip back on. However, an application that attempts to go directly to the serial chip will wind up talking to the chip when it is turned off, resulting in a loss of communication.

#### Sound input/output hardware

Details on the sound system implementation are provided in the section

"Sound Interface" later in this chapter. The sound interface uses an enhanced version of the Apple Sound Chip (ASC) together with the DFAC to provide compatibility with the overall Macintosh sound input/output strategy. If your application uses the Macintosh Sound Manager calls and does not try to access the ASC hardware directly, it will work as documented.

# On-board mathematics coprocessor (FPU)

The 68882 FPU is a standard feature of the Macintosh PowerBook 170 computer but is not supported on the Macintosh PowerBook 140 computer. To ensure that your application is compatible with the Macintosh PowerBook 170, the Macintosh PowerBook 140, and future Macintosh computers that do not have FPUs, use the Gestalt Manager. Using the Gestalt Manager allows you to determine the exact configuration of the machine on which you are running.

If your application is provided in two versions, one that uses SANE (Standard Apple Numerics Environment) software and another that requires the FPU hardware to perform its numeric calculations, or if the application makes a conditional branch to execute floating-point instructions directly, then your application should check first for the presence of an FPU.

#### Hardware overview

This section provides a functional description of the processor, memory, general logic, and I/O (input/output) interface systems. Emphasis is placed on those systems that are new or different from those of the earlier Macintosh Portable and other members of the Macintosh computer family.

**Important** Memory sizes, addresses, and other data are specific to each type of Macintosh computer and are provided for informational purposes only. To ensure that your application software maintains compatibility across the Macintosh line and to allow for future hardware changes, you are strongly advised to use the Macintosh Toolbox and Operating System routines wherever provided. In particular, never use absolute addresses to access hardware, because these addresses are different on different models. ◆

# Main processor

The 68030 microprocessors used in the Macintosh PowerBook 140 and Macintosh PowerBook 170 run at system clock rates of 16 MHz and 25 MHz, respectively. The 68030 includes a built-in MMU (memory management unit) that performs the necessary memory-mapping functions. Floating-point operations in the Macintosh PowerBook 170 are provided by the 68882 mathematics coprocessor FPU. The Macintosh PowerBook 140 does not include an FPU.

## Memory mapping

Two memory address-mapping modes, a 24-bit mode and a 32-bit mode, are implemented. This allows older software to use the 24-bit address space and new software to use the full 32-bit address space. Figure 1-2 shows the main 32-bit memory map and the 32-bit I/O memory map decode of the system I/O address space from \$5000 0000 to \$6000 0000. Figure 1-3 compares the system's main 32-bit memory map with the 24-bit memory map. Notice in Figure 1-3 that video space resides at location \$FEE0 0000 (32-bit mode) or \$E0 0000 (24-bit mode) and not in either RAM or I/O space. Also, you can access the I/O space in 32-bit mode while maintaining a 24-bit mode offset of \$F0 0000 for compatibility. This is because all I/O devices wrap into \$Fx xxxx space.

# • **Figure 1-2** 32-bit memory and detailed I/O map

|            |                  | /        | Expansion I/O s  | \$6000 0             |

|------------|------------------|----------|------------------|----------------------|

|            |                  | /        | (no DSACKs)      | \$5400 O             |

|            |                  | /        | Reserv           | \$5100 O             |

| <b>A</b>   |                  | _ /      | Reserv           |                      |

| \$FFFF FI  | Reserv           | /        | Reserv           | \$5010 0<br>\$500C 0 |

| \$FEFF FFL | Video R/         | /        | CPU GLU regis    | \$5000 0             |

| \$FEE0 0   | Video R <i>F</i> | /        | Reserv           | \$5008 0<br>\$5004 0 |

|            |                  | /        | Reserv           | \$5003 0             |

|            | D                | /        | Reserv           | \$5002 E             |

|            | Reserv           | /        | Reserv           | \$5002 C             |

|            |                  | /        | Reserv           | \$5002 A             |

|            |                  | [/       | Reserv           | \$5002 8             |

| \$6000 0   | 1/0              | ľ        | Reserv           | \$5002 6             |

| \$5000 0   | I/O              |          | Reserv           | \$5002 4             |

|            | Reserv           | \ .      | Reserv           | \$5002 2             |

| \$4400 0   | RON              | <u> </u> | Reserv           | \$5002 0             |

| \$4000 0   | ROV              | <i>i</i> | Reserv           | \$5001 E             |

|            |                  | ,        | Reserv           | \$5001 C             |

|            | Expansio         | 1        | Reserv<br>Reserv | \$5001 A             |

|            | RAM              | ,        |                  | <sub></sub> \$5001 8 |

|            |                  | \        | SWII<br>Sound    | \$5001 6             |

|            |                  | ,        | SCSI (non D      | \$5001 4             |

| \$0400 0   |                  | \        | SCSI (normal r   | \$5001 2             |

|            | (Wrap)           | Ì        | Reserved (SCSI   | \$5001 0             |

| \$0080 0   | RAN              | \        | Reserved (SCC    | \$5000 E             |

|            | 8 MB maximum,    | \ \      | Reserved (VIA2   | \$5000 C             |

| \$0000 0(  | one continuous b | ,        | Reserved (VIA1   | 55000 A              |

|            | 1                | ,        | SCSI (DMA with   | \$5000 8             |

|            |                  | , .      | SC(              | \$5000 6<br>\$5000 4 |

|            |                  | / .      | VIA              | \$5000 4             |

|            |                  | \        | VIA              | \$5000 2             |

|            |                  | 4        |                  | ι ΨΟΟΟΟ Ο            |

# • **Figure 1-3** 32-bit and 24-bit memory maps

# 32-bit memory map

24-bit memory map

| \$FFFF FF     |                                          | \$FF FFF[ <sup></sup> |                  |

|---------------|------------------------------------------|-----------------------|------------------|

| \$FEFF FF     | Reserv                                   | \$F0 FFF              | I/O space        |

| \$FEE0 0      | Video R <i>i</i>                         | \$E0 000L             | Video R <i>i</i> |

| <b>ΦΓΕΟ Ο</b> | Reserv                                   | ф <u>го ооог</u> (    | Reserv           |

| \$6000 0      |                                          |                       |                  |

| \$5000 0      | I/O space                                | \$90 000              |                  |

| \$4400 0      | Reserv                                   |                       | ROM              |

|               | RON                                      | \$80 00C              |                  |

| \$4000 0      | Expansio<br>RAM                          |                       | RAM              |

| \$0400 0      |                                          |                       |                  |

| \$0080 0      | (wraț                                    |                       |                  |

| \$0000 0      | RAN<br>8 MB maximum,<br>One continuous I | \$00 000L l           |                  |

#### **Custom integrated circuits**

This section describes the three ASICs (application-specific integrated circuits) that provide the internal logic functions of the computers.

#### **CPU GLU**

The CPU GLU is a custom gate array that accommodates 24-bit mode and 32-bit mode address compatibility, interrupt encoding, and full-power cycling logic implementation. The CPU GLU generates the CPU clocks, DSACK (data acknowledgment) signals, and buffer control signals and serves as the interface to system ROM, RAM, SCC, SCSI, VIA, FPU, SWIM, and DDC integrated circuits. The CPU GLU also supports a Macintosh II–style 32-bit memory map, pseudostatic RAM refresh, and the ability to make noncontiguous memory appear contiguous for RAM sizes of 1 and 4 Mbits.

#### DDC (Display Driver Chip)

The DDC provides the interface to the LCD. Its function is similar to that of the video chip used in the Macintosh Portable, except that the DDC supports FSTN (Film SuperTwist Nematic) displays as well as active matrix (AM) displays. The DDC generates horizontal and vertical synchronization pulses and all other signals necessary to make the flatpanel display work. The DDC also supports its own video 32K x 8-bit SRAM. In addition, the DDC limits the CPU from refreshing the display and thereby allows the CPU to do more useful work.

#### Miscellaneous GLU

The Miscellaneous GLU is a modified version of the Miscellaneous GLU used in the Macintosh Portable. One of the most significant functions of the Miscellaneous GLU chip is emulating the I/O capabilities of a second VIA in a manner similar to that of a Macintosh IIci computer's RBV (RAM-based video) chip. In addition, the Miscellaneous GLU chip provides random logic functions such as modem/serial port muxing, sound power control, and the clock control logic functions associated with the Power Manager, SWIM, and SCC interfaces.

#### **ROM** interface

The new portable computers use a 1 MB 32-bit-clean ROM. This ROM includes some functions similar to those of the Macintosh Portable ROM, such as a new ADB interface and code to support communication with the Power Manager. Backlight control, a true shutdown mode, and improved modem support are all featured in the Power Manager ROM code; however, unlike in the Macintosh Portable, the real-time clock function is not provided by the Power Manager. Instead, these computers use the same serial clock chip and interface logic as are used in the Macintosh Classic computer. These functions are separated from the Power Manager in order to maintain the real-time clock and parameter RAM when the Power Manager chip is off. The ROM also includes 32-bit QuickDraw.

The ROM is implemented as a 256K x 32-bit array consisting physically of two

$256K \times 16$ -bit 40-pin devices with an access time of 150 ns. The ROM array is located in the system memory map between addresses \$4000 0000 and \$4010 0000.

RAM overlay: Immediately after the system is reset or is taken out of the sleep mode, the RAM overlay process is initiated, causing the starting address of the ROM to be located at \$4000 0000 and overlaying the ROM image in RAM address space starting at \$0000 0000. This overlay allows the 68030 processor to address a standard default set of exception vectors and trap addresses as well as a starting address at which to begin executing code. Following the first access to the normal ROM address range, the ROM image at \$0000 0000 is cleared and replaced by RAM.

**ROM** wait states: Access to the ROM from the main processor in the Macintosh PowerBook 170 requires three processor wait states (six clock access cycles at 25 MHz). This relates to a bus cycle time of 240 ns. In the Macintosh PowerBook 140, access to the ROM from the main processor requires two processor wait states (five clock access cycles at 16 MHz). This relates to a bus cycle time of 320 ns.

#### RAM interface

The new portable computers are shipped with 2 MB of PSRAM on the main logic board. The RAM is arranged physically as four 4-Mbit chips of 512K x 8 bits each. In addition, there is an expansion slot that allows RAM to be expanded to a total of 8 MB. The PowerBook 170 is shipped with a 2 MB RAM expansion card in this slot giving that machine a total of 4 MB of RAM. The expansion feature is described in the next section, "RAM Expansion."

RAM is always contiguous because only one size of RAM chip (4 Mbits) is used. As a result, software does not have to size the memory. The RAM array is nominally located in the system memory map between addresses \$0000 0000 and \$0020 0000 (up to \$0080 0000 in an 8 MB system), except following a system reset or sleep cycle, at which time it is overlaid by system ROM. However, the overlay is removed following access to normal ROM space, and the RAM space is then accessible. Both RAM and ROM memory spaces provide DSACK signals to the processor even if memory is not actually installed.

RAM wait states: Access to the RAM from the main processor requires 100 ns PSRAM. The Macintosh PowerBook 170 requires two processor wait states (five clock cycles per RAM access), and the Macintosh PowerBook 170 requires one processor wait state (four clock cycles per RAM access). The PSRAM, unlike the SRAM in the original Macintosh Portable, must be refreshed. The CPU GLU custom chip includes special circuitry that performs the refresh function.

**Battery backup:** Both main and expansion RAM memories are backed up when the computer is in the sleep mode. This means that when the computer is not in use, the contents of the memory array are retained as long as the battery remains charged.

# RAM expansion

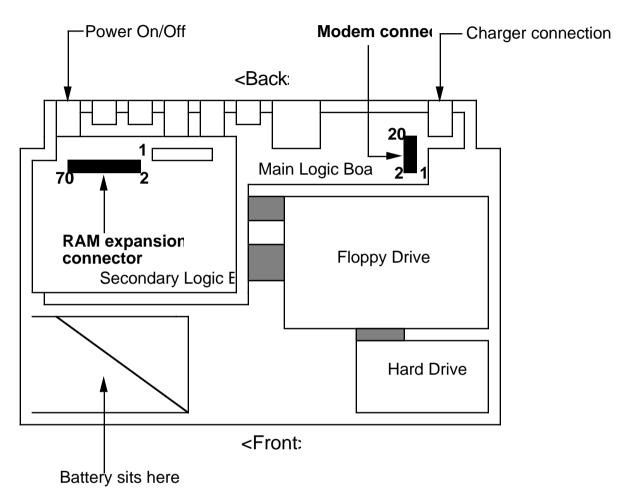

The secondary logic board (often referred to as the daughterboard) contains a 70-pin RAM expansion connector (slot) that supports RAM expansion card sizes of 2 MB, 4 MB, and 6 MB. The location and orientation of the connector is shown in Figure 1-4.

• Note: If you design a RAM expansion card correctly, it will also work in the Macintosh PowerBook 100 computer, a new 68HC000-based portable computer. The 68030 processor in the Macintosh PowerBook 140 and the Macintosh PowerBook 170 has a 32-bit data bus, whereas the 68HC000 processor in the Macintosh PowerBook 100 has only a 16-bit data bus. You should design the expansion card as a 32-bit device, but if you correctly partition the data lines and chip select lines on the card, you can use the same card in any of these machines without loss of performance. The card should have 32 data lines coming out to its connector, and the chip select lines for the upper 16 data bits and the lower 16 data bits should be separated to allow for individual selection of either the upper 16 bits or the lower 16 bits of data. The separated chip select lines are necessary for the 68HC000-based machine because it can get access to only 16 bits at a time. A 68030-based machine does not require separated chip select lines because it has a 32-bit data bus; therefore, the lines are tied back together on the computer's main logic board.

# • Figure 1-4 Location of modem and RAM expansion connectors

As is the case with the permanent ROM, only 4-Mbit chips are used for expansion RAM. For example, a 4 MB RAM expansion card has eight 4-Mbit PSRAMs (512K x 8-bit chips arranged as two banks of 32 bits), and a 6 MB card has twelve 4-Mbit PSRAMs (512K x 8-bit chips arranged as three banks of 32 bits). Access and cycle times for these devices are 100 ns.

♦ Important If you are designing a RAM expansion card for these computers, you do not have to include logic for address decode or chip select because all of the required signals (address, data, chip select, and control) are available at the RAM expansion connector. Data buffering is also provided to compensate for the extra loading caused by the RAM expansion card chips. •

#### RAM expansion connector signals

Table 1-1 provides the pin number, name, and description of each of the RAM expansion connector signals.

♦ *Note*: If you are designing a RAM expansion card, you should normally consider pin 49 (/ROM.CS.EXP) as no connection, unless your expansion card includes its own ROM and it is intended to replace system ROM.

| • | Table 1-1 | RAM | expansion | connector | signals |

|---|-----------|-----|-----------|-----------|---------|

|---|-----------|-----|-----------|-----------|---------|

| Pin nun | nber Signal name | Signal description          |             |

|---------|------------------|-----------------------------|-------------|

| 1       | GND              | Ground                      |             |

| 2       | GND              | Ground                      |             |

| 3       | A20              | Address bit 20 (unbuffered) |             |

| 4       | A17              | Address bit 17 (unbuffered) |             |

| 5       | A18              | Address bit 18 (unbuffered) |             |

| 6       | A19              | Address bit 19 (unbuffered) |             |

| 7       | A16              | Address bit 16 (unbuffered) |             |

| 8       | /LLW             | Lower write byte            |             |

| 9       | A14              | Address bit 14 (unbuffered) |             |

| 10      | /LUW             | Lower middle write byte     |             |

| 11      | A9               | Address bit 9 (unbuffered)  |             |

|         |                  |                             | (continued) |

• Table 1-1 RAM expansion connector signals (continued)

| Pin nu | mber Signal name | Signal description                             |

|--------|------------------|------------------------------------------------|

| 12     | A15              | Address bit 15 (unbuffered)                    |

| 13     | A8               | Address bit 8 (unbuffered)                     |

| 14     | A10              | Address bit 10 (unbuffered)                    |

| 15     | A7               | Address bit 7 (unbuffered)                     |

| 16     | A11              | Address bit 11 (unbuffered)                    |

| 17     | A6               | Address bit 6 (unbuffered)                     |

| 18     | A13              | Address bit 13 (unbuffered)                    |

| 19     | A5               | Address bit 5 (unbuffered)                     |

| 20     | /RAM.OE          | RAM output enable and refresh for 4 MB PSRAMs  |

| 21     | A4               | Address bit 4 (unbuffered)                     |

| 22     | A12              | Address bit 12 (unbuffered)                    |

| 23     | A3               | Address bit 3 (unbuffered)                     |

| 24     | /RAMACS1         | PSRAM bank chip select bit 1                   |

| 25     | A2               | Address bit 2 (unbuffered)                     |

| 26     | MDATA23          | Bit 23, 32-bit-wide memory data bus (buffered) |

| 27     | MDATA16          | Bit 16, 32-bit-wide memory data bus (buffered) |

| 28     | MDATA22          | Bit 22, 32-bit-wide memory data bus (buffered) |

| 29     | MDATA17          | Bit 17, 32-bit-wide memory data bus (buffered) |

| 30     | MDATA21          | Bit 21, 32-bit-wide memory data bus (buffered) |

| 31     | MDATA18          | Bit 18, 32-bit-wide memory data bus (buffered) |

| 32     | MDATA20          | Bit 20, 32-bit-wide memory data bus (buffered) |

| 33     | GND              | Ground                                         |

| 34     | /RAMACS1         | PSRAM bank chip select bit 1                   |

| 35     | MDATA4           | Bit 4, 32-bit-wide memory data bus (buffered)  |

| 36     | MDATA19          | Bit 19, 32-bit-wide memory data bus (buffered) |

| 37     | MDATA2           | Bit 2, 32-bit-wide memory data bus (buffered)  |

| 38     | MDATA3           | Bit 3, 32-bit-wide memory data bus (buffered)  |

| 39     | MDATA0           | Bit 0, 32-bit-wide memory data bus (buffered)  |

| 40     | MDATA1           | Bit 1, 32-bit-wide memory data bus (buffered)  |

| 41     | MDATA7           | Bit 7, 32-bit-wide memory data bus (buffered)  |

| 42     | MDATA6           | Bit 6, 32-bit-wide memory data bus (buffered)  |

| 43     | +5V.SH           | +5 V (RAM power/shutdown plane)                |

| 44     | MDATA5           | Bit 5, 32-bit-wide memory data bus (buffered)  |

|        |                  | (continued)                                    |

#### • **Table 1-1** RAM expansion connector signals (continued)

| 45 /RAMACS3 PSRAM bank chip select bit 3 46 +5V.SH +5 V (RAM power/shutdown plane) 47 /UUW Upper write byte 48 /ULW Upper middle write byte 49 /ROM.CS.EXP ROM chip select 50 /RAMACS2 PSRAM bank chip select bit 2 51 /RAMACS3 PSRAM bank chip select bit 3 52 +5V.SH +5 V (RAM power/shutdown plane) 53 MDATA27 Bit 27, 32-bit-wide memory data bus (buffered) 54 MDATA28 Bit 28, 32-bit-wide memory data bus (buffered) 55 MDATA14 Bit 14, 32-bit-wide memory data bus (buffered) 56 MDATA29 Bit 29, 32-bit-wide memory data bus (buffered) 57 MDATA24 Bit 24, 32-bit-wide memory data bus (buffered) 58 MDATA30 Bit 30, 32-bit-wide memory data bus (buffered) 60 MDATA25 Bit 25, 32-bit-wide memory data bus (buffered) 61 MDATA26 Bit 26, 32-bit-wide memory data bus (buffered) 62 MDATA15 Bit 13, 32-bit-wide memory data bus (buffered) 63 MDATA13 Bit 13, 32-bit-wide memory data bus (buffered) 64 MDATA8 Bit 8, 32-bit-wide memory data bus (buffered) 65 MDATA12 Bit 12, 32-bit-wide memory data bus (buffered) 66 MDATA9 Bit 9, 32-bit-wide memory data bus (buffered) 67 MDATA11 Bit 11, 32-bit-wide memory data bus (buffered) 68 MDATA10 Bit 10, 32-bit-wide memory data bus (buffered) 69 GND Ground 70 /RAMACS2 PSRAM bank chip select bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pin number | Signal name | Signal description                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|------------------------------------------------|

| 47 /UUW Upper write byte 48 /ULW Upper middle write byte 49 /ROM.CS.EXP ROM chip select 50 /RAMACS2 PSRAM bank chip select bit 2 51 /RAMACS3 PSRAM bank chip select bit 3 52 +5V.SH +5 V (RAM power/shutdown plane) 53 MDATA27 Bit 27, 32-bit-wide memory data bus (buffered) 54 MDATA28 Bit 28, 32-bit-wide memory data bus (buffered) 55 MDATA14 Bit 14, 32-bit-wide memory data bus (buffered) 56 MDATA29 Bit 29, 32-bit-wide memory data bus (buffered) 57 MDATA24 Bit 24, 32-bit-wide memory data bus (buffered) 58 MDATA30 Bit 30, 32-bit-wide memory data bus (buffered) 59 MDATA25 Bit 25, 32-bit-wide memory data bus (buffered) 60 MDATA31 Bit 31, 32-bit-wide memory data bus (buffered) 61 MDATA26 Bit 26, 32-bit-wide memory data bus (buffered) 62 MDATA15 Bit 15, 32-bit-wide memory data bus (buffered) 63 MDATA13 Bit 13, 32-bit-wide memory data bus (buffered) 64 MDATA8 Bit 8, 32-bit-wide memory data bus (buffered) 65 MDATA12 Bit 12, 32-bit-wide memory data bus (buffered) 66 MDATA9 Bit 9, 32-bit-wide memory data bus (buffered) 67 MDATA11 Bit 11, 32-bit-wide memory data bus (buffered) 68 MDATA10 Bit 10, 32-bit-wide memory data bus (buffered) 69 GND Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 45         | /RAMACS3    | PSRAM bank chip select bit 3                   |

| 48 /ULW Upper middle write byte 49 /ROM.CS.EXP ROM chip select 50 /RAMACS2 PSRAM bank chip select bit 2 51 /RAMACS3 PSRAM bank chip select bit 3 52 +5V.SH +5 V (RAM power/shutdown plane) 53 MDATA27 Bit 27, 32-bit-wide memory data bus (buffered) 54 MDATA28 Bit 28, 32-bit-wide memory data bus (buffered) 55 MDATA14 Bit 14, 32-bit-wide memory data bus (buffered) 56 MDATA29 Bit 29, 32-bit-wide memory data bus (buffered) 57 MDATA24 Bit 24, 32-bit-wide memory data bus (buffered) 58 MDATA30 Bit 30, 32-bit-wide memory data bus (buffered) 59 MDATA25 Bit 25, 32-bit-wide memory data bus (buffered) 60 MDATA31 Bit 31, 32-bit-wide memory data bus (buffered) 61 MDATA26 Bit 26, 32-bit-wide memory data bus (buffered) 62 MDATA15 Bit 15, 32-bit-wide memory data bus (buffered) 63 MDATA13 Bit 33, 32-bit-wide memory data bus (buffered) 64 MDATA8 Bit 8, 32-bit-wide memory data bus (buffered) 65 MDATA12 Bit 12, 32-bit-wide memory data bus (buffered) 66 MDATA9 Bit 9, 32-bit-wide memory data bus (buffered) 67 MDATA11 Bit 11, 32-bit-wide memory data bus (buffered) 68 MDATA10 Bit 10, 32-bit-wide memory data bus (buffered) 69 GND Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 46         | +5V.SH      | +5 V (RAM power/shutdown plane)                |

| 49 /ROM.CS.EXP ROM chip select 50 /RAMACS2 PSRAM bank chip select bit 2 51 /RAMACS3 PSRAM bank chip select bit 3 52 +5V.SH +5 V (RAM power/shutdown plane) 53 MDATA27 Bit 27, 32-bit-wide memory data bus (buffered) 54 MDATA28 Bit 28, 32-bit-wide memory data bus (buffered) 55 MDATA14 Bit 14, 32-bit-wide memory data bus (buffered) 56 MDATA29 Bit 29, 32-bit-wide memory data bus (buffered) 57 MDATA24 Bit 24, 32-bit-wide memory data bus (buffered) 58 MDATA30 Bit 30, 32-bit-wide memory data bus (buffered) 59 MDATA25 Bit 25, 32-bit-wide memory data bus (buffered) 60 MDATA31 Bit 31, 32-bit-wide memory data bus (buffered) 61 MDATA26 Bit 26, 32-bit-wide memory data bus (buffered) 62 MDATA15 Bit 15, 32-bit-wide memory data bus (buffered) 63 MDATA13 Bit 13, 32-bit-wide memory data bus (buffered) 64 MDATA8 Bit 8, 32-bit-wide memory data bus (buffered) 65 MDATA12 Bit 12, 32-bit-wide memory data bus (buffered) 66 MDATA9 Bit 9, 32-bit-wide memory data bus (buffered) 67 MDATA11 Bit 11, 32-bit-wide memory data bus (buffered) 68 MDATA10 Bit 10, 32-bit-wide memory data bus (buffered) 69 GND Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47         | /UUW        | Upper write byte                               |

| PSRAM bank chip select bit 2  PSRAM bank chip select bit 3  PSRAM bank chip select bit 2  PSRAM bank chip select bit 3  PSRAM bank chip select bit 3  PSRAM bank chip select bit 2  PSRAM bank chip selct bit 3  PSRAM bank chip selct bit 4  Bit 27, 32-bit-wide memory data bus (buffered)  Bit 13, 32-bit-wide memory data bus (buffered)  Bit 11, 32-bit-wide memory data bus (buffered)  Bit 12, 32-bit-wide memory data bus (buffered) | 48         | /ULW        | Upper middle write byte                        |

| PSRAM bank chip select bit 3  72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 49         | /ROM.CS.EXP | ROM chip select                                |

| 52 +5V.SH +5 V (RAM power/shutdown plane) 53 MDATA27 Bit 27, 32-bit-wide memory data bus (buffered) 54 MDATA28 Bit 28, 32-bit-wide memory data bus (buffered) 55 MDATA14 Bit 14, 32-bit-wide memory data bus (buffered) 56 MDATA29 Bit 29, 32-bit-wide memory data bus (buffered) 57 MDATA24 Bit 24, 32-bit-wide memory data bus (buffered) 58 MDATA30 Bit 30, 32-bit-wide memory data bus (buffered) 59 MDATA25 Bit 25, 32-bit-wide memory data bus (buffered) 60 MDATA31 Bit 31, 32-bit-wide memory data bus (buffered) 61 MDATA26 Bit 26, 32-bit-wide memory data bus (buffered) 62 MDATA15 Bit 15, 32-bit-wide memory data bus (buffered) 63 MDATA13 Bit 13, 32-bit-wide memory data bus (buffered) 64 MDATA8 Bit 8, 32-bit-wide memory data bus (buffered) 65 MDATA12 Bit 12, 32-bit-wide memory data bus (buffered) 66 MDATA9 Bit 9, 32-bit-wide memory data bus (buffered) 67 MDATA11 Bit 11, 32-bit-wide memory data bus (buffered) 68 MDATA10 Bit 10, 32-bit-wide memory data bus (buffered) 69 GND Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 50         | /RAMACS2    | PSRAM bank chip select bit 2                   |

| MDATA28 Bit 27, 32-bit-wide memory data bus (buffered) Bit 28, 32-bit-wide memory data bus (buffered) MDATA14 Bit 14, 32-bit-wide memory data bus (buffered) MDATA29 Bit 29, 32-bit-wide memory data bus (buffered) MDATA24 Bit 24, 32-bit-wide memory data bus (buffered) MDATA30 Bit 30, 32-bit-wide memory data bus (buffered) MDATA25 Bit 25, 32-bit-wide memory data bus (buffered) MDATA31 Bit 31, 32-bit-wide memory data bus (buffered) MDATA26 Bit 26, 32-bit-wide memory data bus (buffered) MDATA15 Bit 15, 32-bit-wide memory data bus (buffered) MDATA13 Bit 13, 32-bit-wide memory data bus (buffered) MDATA14 Bit 13, 32-bit-wide memory data bus (buffered) MDATA15 Bit 13, 32-bit-wide memory data bus (buffered) MDATA16 Bit 12, 32-bit-wide memory data bus (buffered) MDATA17 Bit 12, 32-bit-wide memory data bus (buffered) MDATA19 Bit 9, 32-bit-wide memory data bus (buffered) MDATA11 Bit 11, 32-bit-wide memory data bus (buffered) MDATA10 Bit 10, 32-bit-wide memory data bus (buffered) GND Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 51         | /RAMACS3    | PSRAM bank chip select bit 3                   |

| 54MDATA28Bit 28, 32-bit-wide memory data bus (buffered)55MDATA14Bit 14, 32-bit-wide memory data bus (buffered)56MDATA29Bit 29, 32-bit-wide memory data bus (buffered)57MDATA24Bit 24, 32-bit-wide memory data bus (buffered)58MDATA30Bit 30, 32-bit-wide memory data bus (buffered)59MDATA25Bit 25, 32-bit-wide memory data bus (buffered)60MDATA31Bit 31, 32-bit-wide memory data bus (buffered)61MDATA26Bit 26, 32-bit-wide memory data bus (buffered)62MDATA15Bit 15, 32-bit-wide memory data bus (buffered)63MDATA13Bit 13, 32-bit-wide memory data bus (buffered)64MDATA8Bit 8, 32-bit-wide memory data bus (buffered)65MDATA12Bit 12, 32-bit-wide memory data bus (buffered)66MDATA9Bit 9, 32-bit-wide memory data bus (buffered)67MDATA11Bit 11, 32-bit-wide memory data bus (buffered)68MDATA10Bit 10, 32-bit-wide memory data bus (buffered)69GNDGround                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 52         | +5V.SH      | +5 V (RAM power/shutdown plane)                |

| MDATA14 Bit 14, 32-bit-wide memory data bus (buffered) Bit 29, 32-bit-wide memory data bus (buffered) MDATA24 Bit 24, 32-bit-wide memory data bus (buffered) MDATA30 Bit 30, 32-bit-wide memory data bus (buffered) MDATA25 Bit 25, 32-bit-wide memory data bus (buffered) MDATA31 Bit 31, 32-bit-wide memory data bus (buffered) MDATA26 Bit 26, 32-bit-wide memory data bus (buffered) MDATA15 Bit 15, 32-bit-wide memory data bus (buffered) MDATA13 Bit 13, 32-bit-wide memory data bus (buffered) MDATA14 Bit 13, 32-bit-wide memory data bus (buffered) MDATA8 Bit 8, 32-bit-wide memory data bus (buffered) MDATA12 Bit 12, 32-bit-wide memory data bus (buffered) MDATA9 Bit 9, 32-bit-wide memory data bus (buffered) MDATA11 Bit 11, 32-bit-wide memory data bus (buffered) MDATA11 Bit 11, 32-bit-wide memory data bus (buffered) MDATA10 Bit 10, 32-bit-wide memory data bus (buffered) GOND Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53         | MDATA27     | Bit 27, 32-bit-wide memory data bus (buffered) |

| Bit 29, 32-bit-wide memory data bus (buffered)  MDATA24  Bit 24, 32-bit-wide memory data bus (buffered)  MDATA30  Bit 30, 32-bit-wide memory data bus (buffered)  MDATA25  Bit 25, 32-bit-wide memory data bus (buffered)  MDATA31  Bit 31, 32-bit-wide memory data bus (buffered)  MDATA26  Bit 26, 32-bit-wide memory data bus (buffered)  MDATA15  Bit 15, 32-bit-wide memory data bus (buffered)  MDATA13  Bit 13, 32-bit-wide memory data bus (buffered)  MDATA14  Bit 13, 32-bit-wide memory data bus (buffered)  MDATA8  Bit 8, 32-bit-wide memory data bus (buffered)  MDATA12  Bit 12, 32-bit-wide memory data bus (buffered)  MDATA9  Bit 9, 32-bit-wide memory data bus (buffered)  MDATA11  Bit 11, 32-bit-wide memory data bus (buffered)  MDATA11  Bit 11, 32-bit-wide memory data bus (buffered)  MDATA10  Bit 10, 32-bit-wide memory data bus (buffered)  GROD  Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54         | MDATA28     | Bit 28, 32-bit-wide memory data bus (buffered) |

| 57 MDATA24 Bit 24, 32-bit-wide memory data bus (buffered) 58 MDATA30 Bit 30, 32-bit-wide memory data bus (buffered) 59 MDATA25 Bit 25, 32-bit-wide memory data bus (buffered) 60 MDATA31 Bit 31, 32-bit-wide memory data bus (buffered) 61 MDATA26 Bit 26, 32-bit-wide memory data bus (buffered) 62 MDATA15 Bit 15, 32-bit-wide memory data bus (buffered) 63 MDATA13 Bit 13, 32-bit-wide memory data bus (buffered) 64 MDATA8 Bit 8, 32-bit-wide memory data bus (buffered) 65 MDATA12 Bit 12, 32-bit-wide memory data bus (buffered) 66 MDATA9 Bit 9, 32-bit-wide memory data bus (buffered) 67 MDATA11 Bit 11, 32-bit-wide memory data bus (buffered) 68 MDATA10 Bit 10, 32-bit-wide memory data bus (buffered) 69 GND Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 55         | MDATA14     | Bit 14, 32-bit-wide memory data bus (buffered) |

| MDATA30 Bit 30, 32-bit-wide memory data bus (buffered) Bit 25, 32-bit-wide memory data bus (buffered) Bit 31, 32-bit-wide memory data bus (buffered) Bit 31, 32-bit-wide memory data bus (buffered) Bit 26, 32-bit-wide memory data bus (buffered) Bit 15, 32-bit-wide memory data bus (buffered) Bit 13, 32-bit-wide memory data bus (buffered) Bit 13, 32-bit-wide memory data bus (buffered) MDATA13 Bit 13, 32-bit-wide memory data bus (buffered) Bit 8, 32-bit-wide memory data bus (buffered) Bit 12, 32-bit-wide memory data bus (buffered) Bit 9, 32-bit-wide memory data bus (buffered) MDATA11 Bit 11, 32-bit-wide memory data bus (buffered) Bit 10, 32-bit-wide memory data bus (buffered) GND Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 56         | MDATA29     | Bit 29, 32-bit-wide memory data bus (buffered) |

| MDATA25 Bit 25, 32-bit-wide memory data bus (buffered) MDATA31 Bit 31, 32-bit-wide memory data bus (buffered) Bit 26, 32-bit-wide memory data bus (buffered) Bit 15, 32-bit-wide memory data bus (buffered) Bit 13, 32-bit-wide memory data bus (buffered) Bit 13, 32-bit-wide memory data bus (buffered) Bit 13, 32-bit-wide memory data bus (buffered) Bit 8, 32-bit-wide memory data bus (buffered) Bit 12, 32-bit-wide memory data bus (buffered) Bit 12, 32-bit-wide memory data bus (buffered) Bit 11, 32-bit-wide memory data bus (buffered) Bit 11, 32-bit-wide memory data bus (buffered) Bit 10, 32-bit-wide memory data bus (buffered) GND Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 57         | MDATA24     | Bit 24, 32-bit-wide memory data bus (buffered) |

| MDATA31 Bit 31, 32-bit-wide memory data bus (buffered) Bit 26, 32-bit-wide memory data bus (buffered) MDATA15 Bit 15, 32-bit-wide memory data bus (buffered) MDATA13 Bit 13, 32-bit-wide memory data bus (buffered) Bit 13, 32-bit-wide memory data bus (buffered) MDATA8 Bit 8, 32-bit-wide memory data bus (buffered) Bit 12, 32-bit-wide memory data bus (buffered) MDATA9 Bit 9, 32-bit-wide memory data bus (buffered) MDATA11 Bit 11, 32-bit-wide memory data bus (buffered) MDATA10 Bit 10, 32-bit-wide memory data bus (buffered) GND Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 58         | MDATA30     | Bit 30, 32-bit-wide memory data bus (buffered) |

| MDATA26 Bit 26, 32-bit-wide memory data bus (buffered) Bit 15, 32-bit-wide memory data bus (buffered) Bit 13, 32-bit-wide memory data bus (buffered) Bit 8, 32-bit-wide memory data bus (buffered) Bit 12, 32-bit-wide memory data bus (buffered) Bit 12, 32-bit-wide memory data bus (buffered) Bit 9, 32-bit-wide memory data bus (buffered) Bit 11, 32-bit-wide memory data bus (buffered) Bit 11, 32-bit-wide memory data bus (buffered) Bit 10, 32-bit-wide memory data bus (buffered) GND Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59         | MDATA25     | Bit 25, 32-bit-wide memory data bus (buffered) |

| MDATA15 Bit 15, 32-bit-wide memory data bus (buffered) Bit 13, 32-bit-wide memory data bus (buffered) MDATA8 Bit 8, 32-bit-wide memory data bus (buffered) Bit 12, 32-bit-wide memory data bus (buffered) MDATA12 Bit 12, 32-bit-wide memory data bus (buffered) MDATA9 Bit 9, 32-bit-wide memory data bus (buffered) MDATA11 Bit 11, 32-bit-wide memory data bus (buffered) MDATA10 Bit 10, 32-bit-wide memory data bus (buffered) GND Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 60         | MDATA31     | Bit 31, 32-bit-wide memory data bus (buffered) |